一 : 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

并行加法器 计算机组成原理07-运算方法--并行加法器

61阅读请您转载分享:

二 : 计算机组成原理07-运算方法--并行加法器

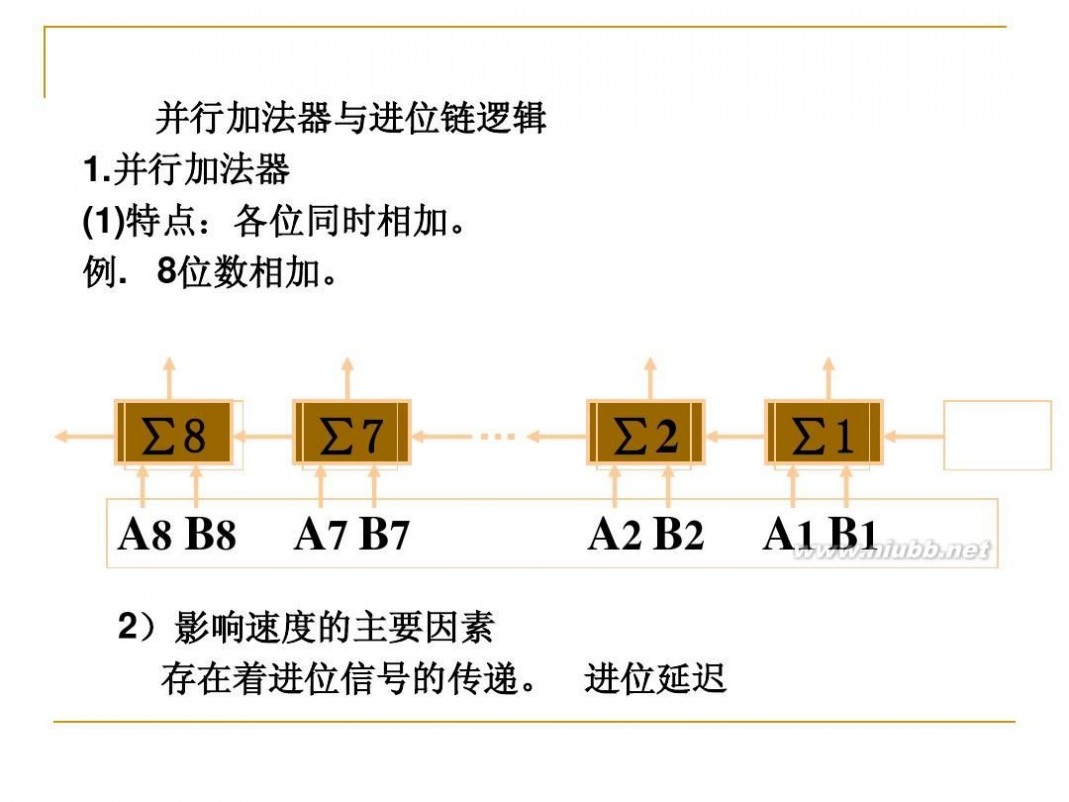

二,并行加法器与进位链逻辑 1.并行加法器 并行加法器 (1)特点:各位同时相加. 特点: 特点 各位同时相加. 位数相加. 例. 8位数相加. 位数相加

1

0

∑8 A8 B8

1 0

1

0

∑7 A7 B7

1 0

1

1

0

∑2 A2 B2

1 0

1

0

∑1 A1 B1

1 0

1

C0

) (2)影响速度的主要因素 存在着进位信号的传递. 存在着进位信号的传递. 进位延迟

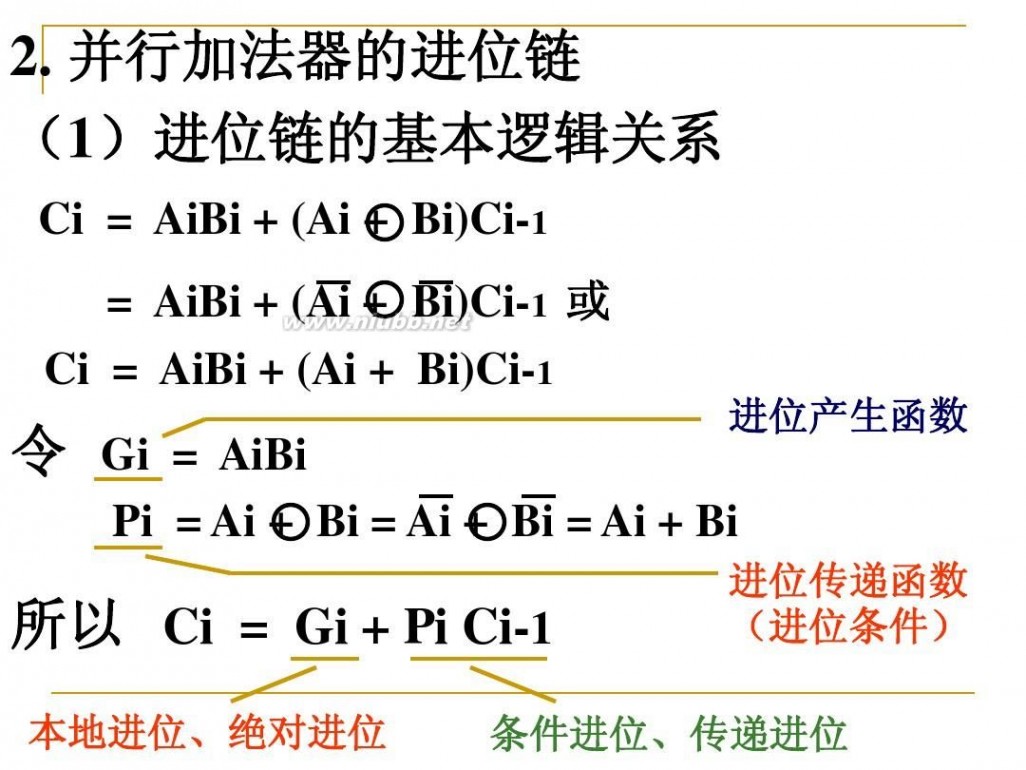

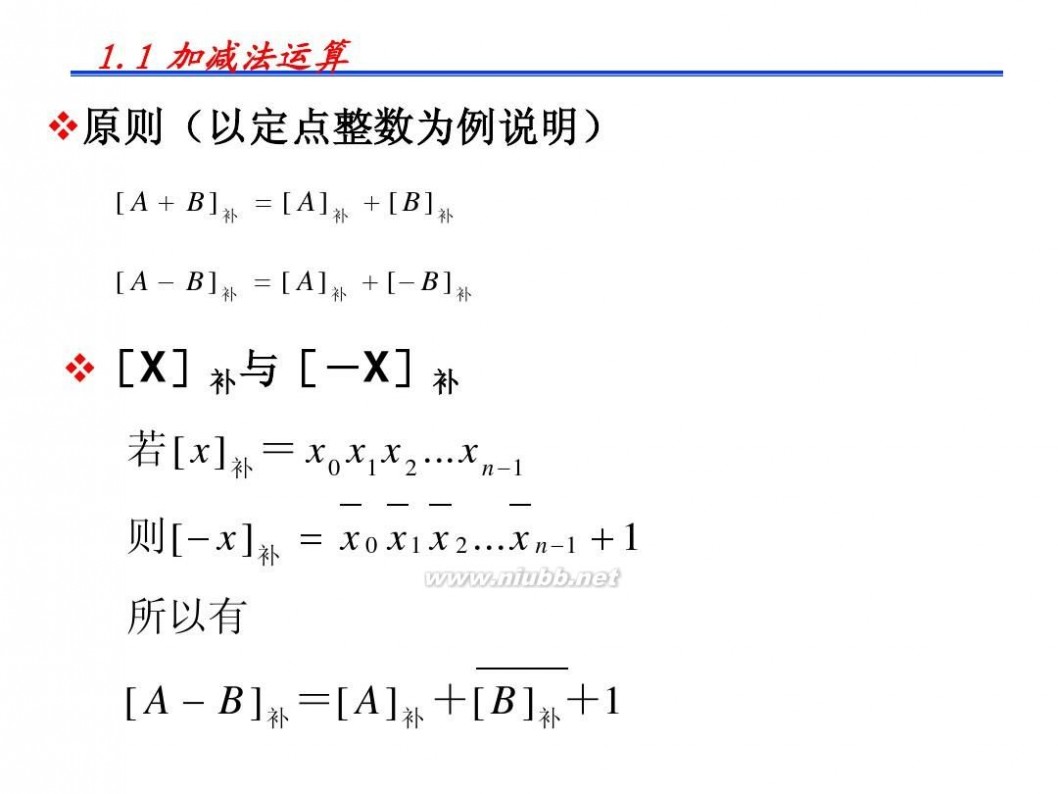

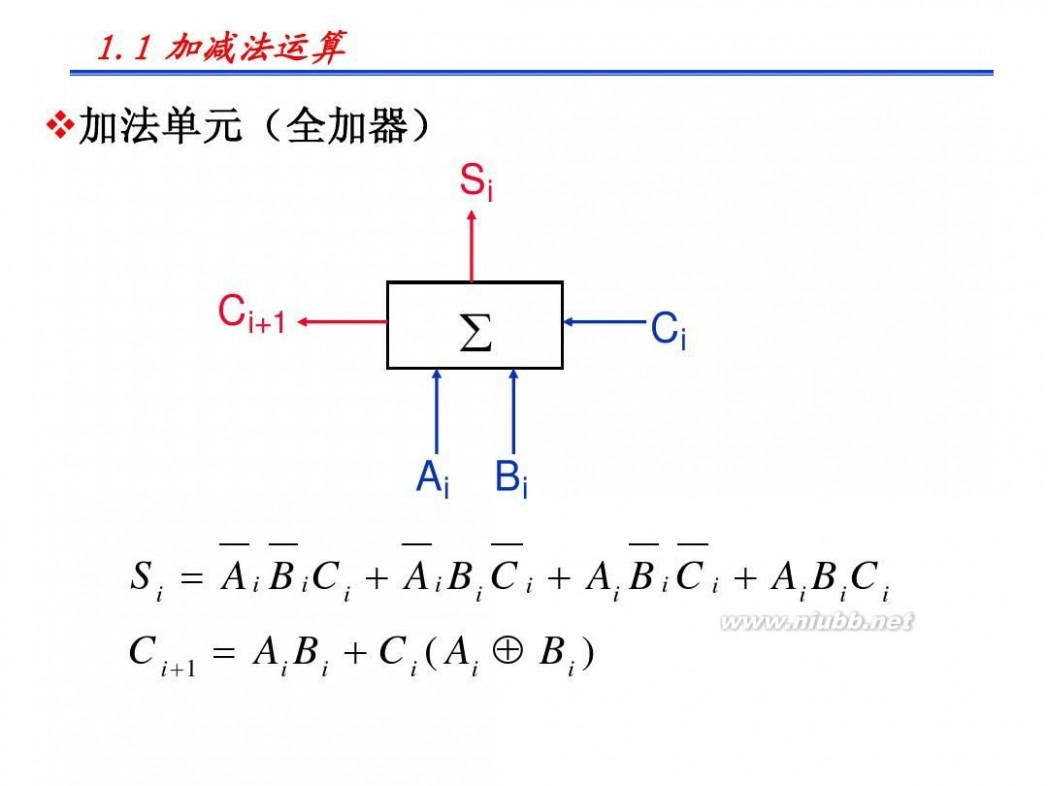

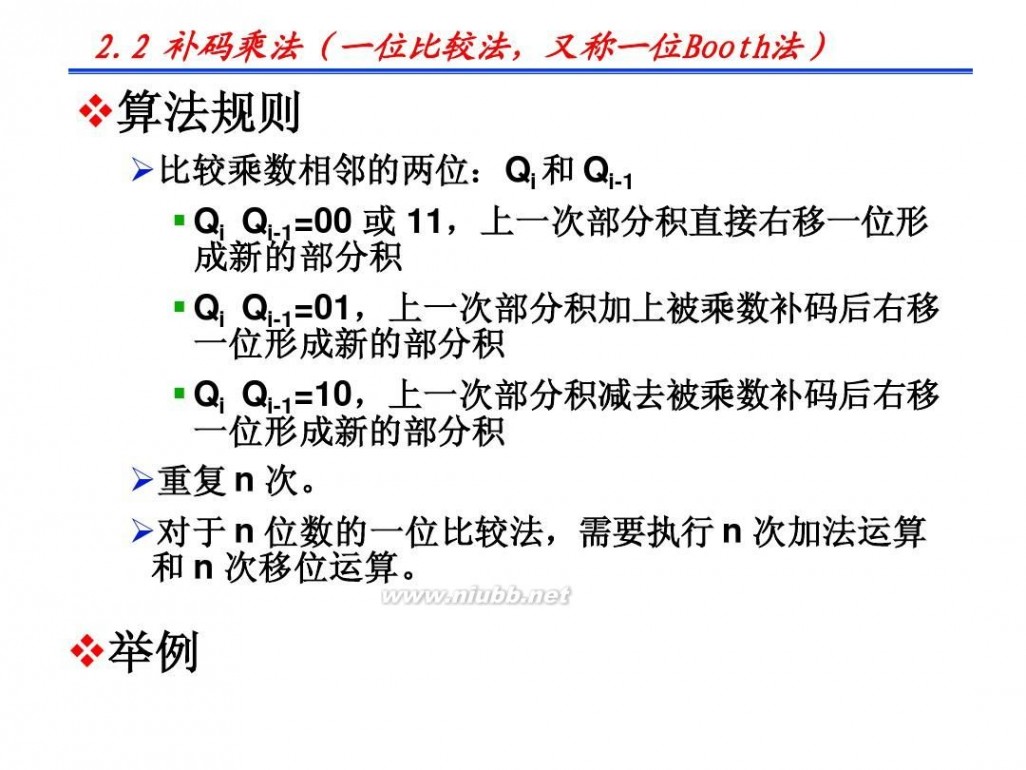

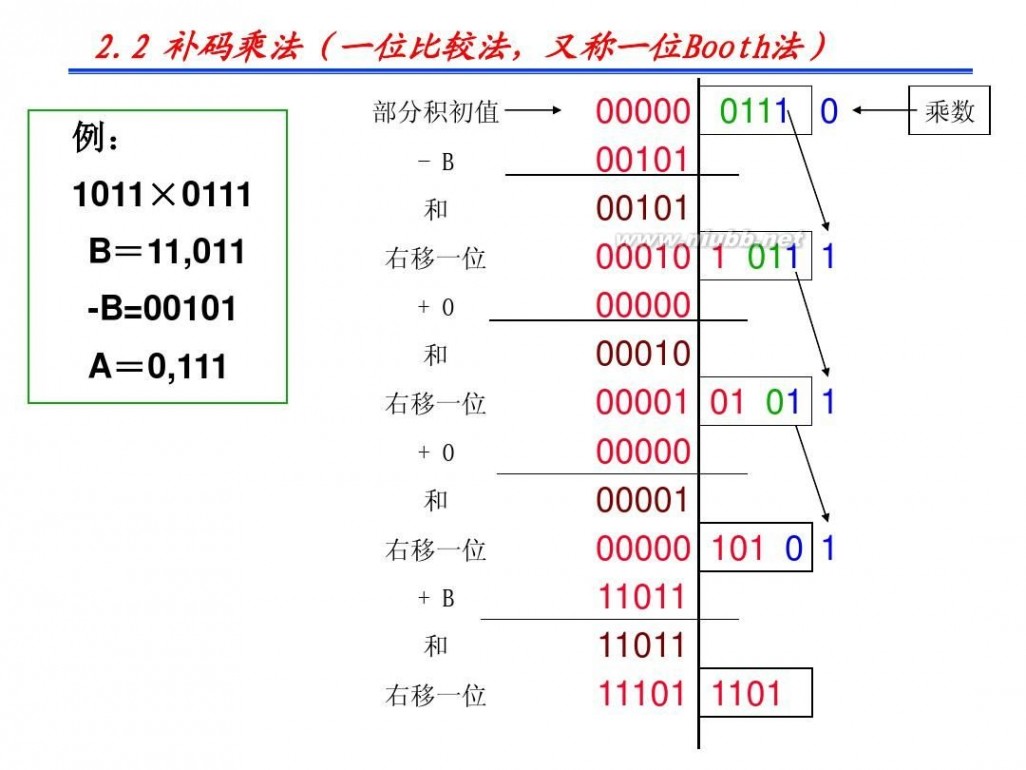

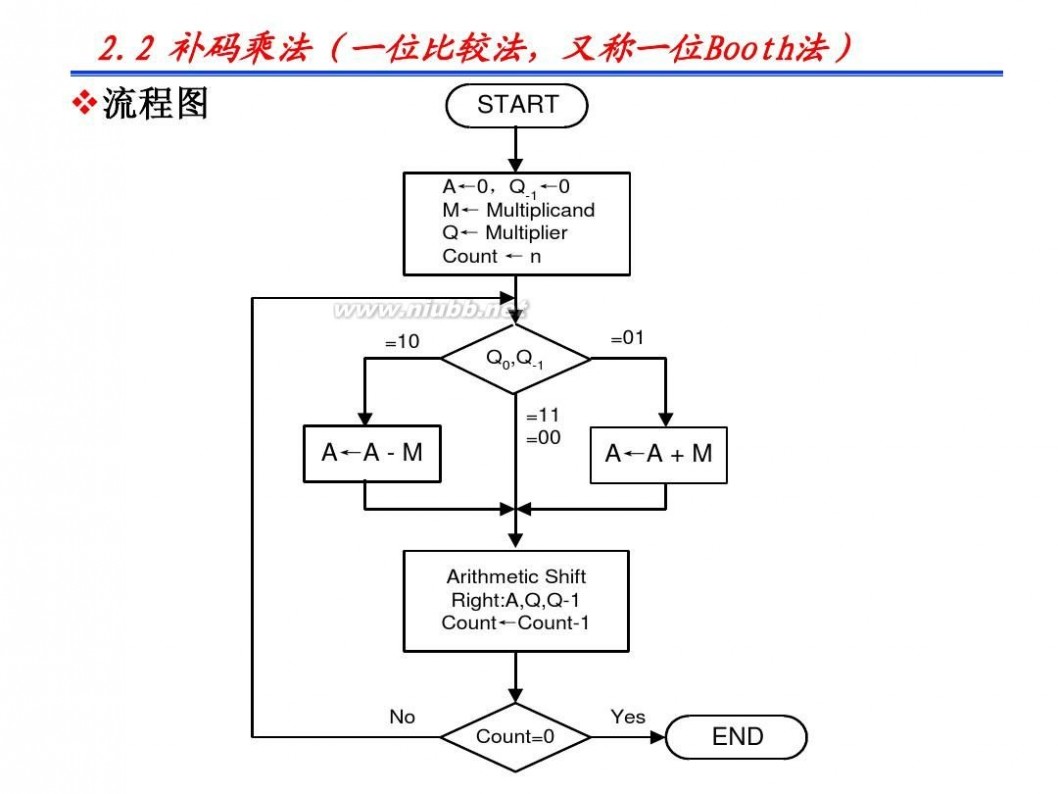

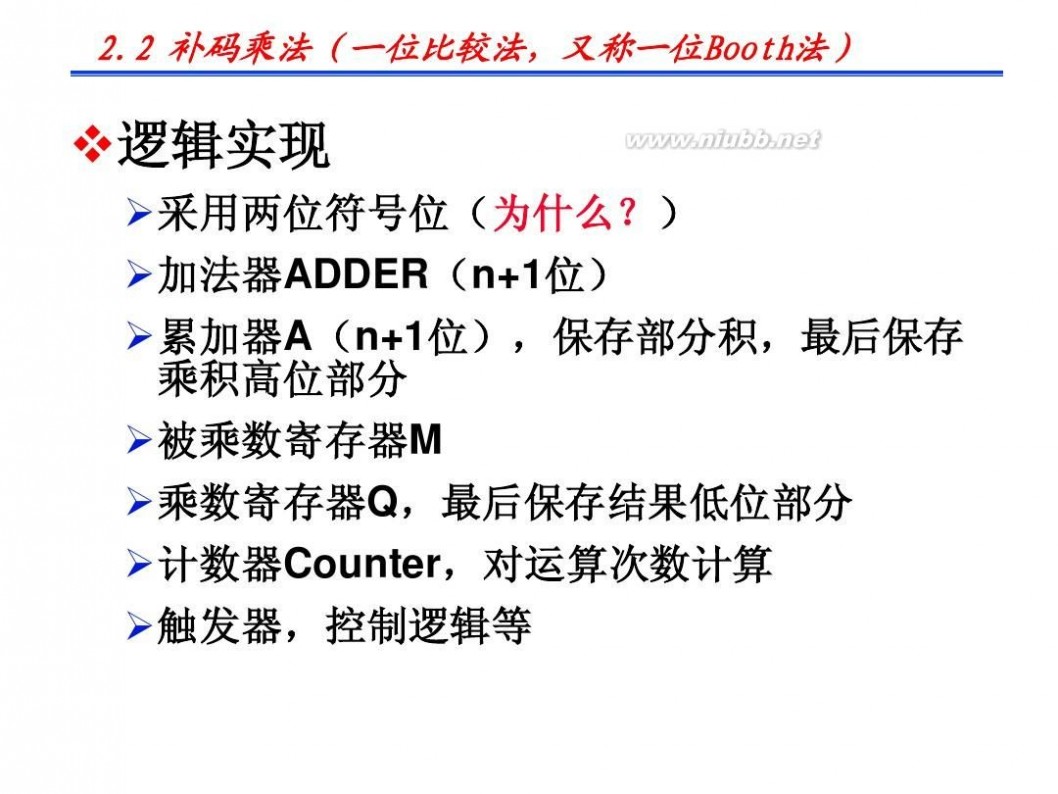

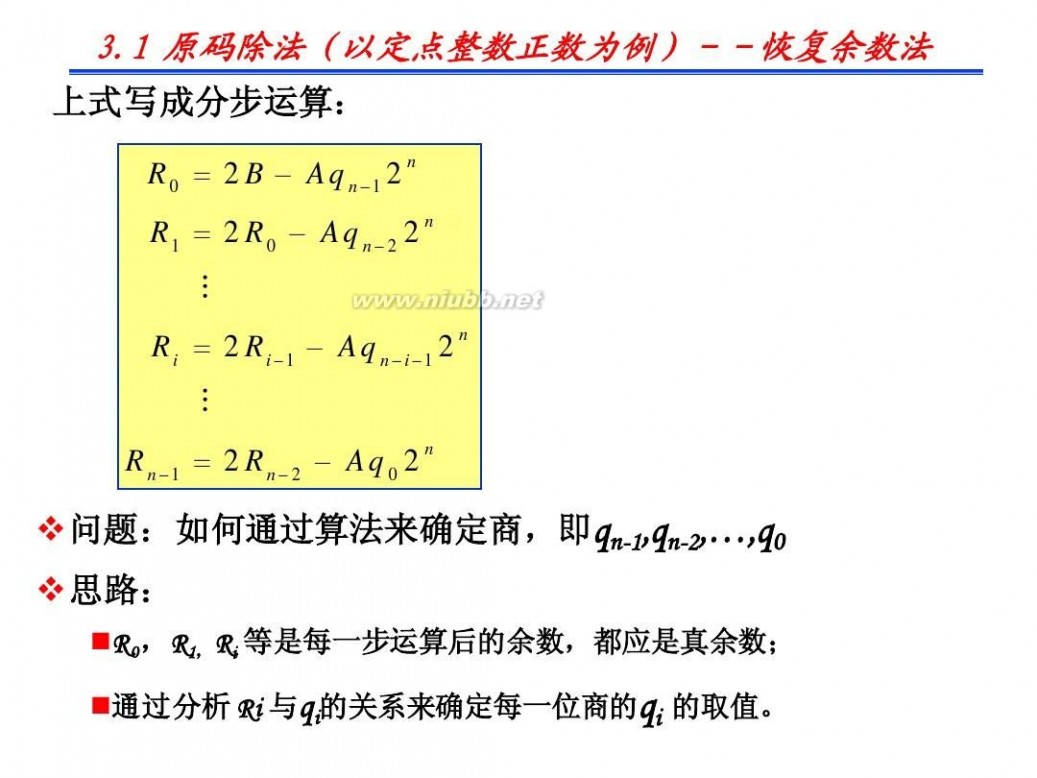

2. 并行加法器的进位链 (1)进位链的基本逻辑关系 )

Ci = AiBi + (Ai + Bi)Ci-1 = AiBi + (Ai + Bi)Ci-1 或 Ci = AiBi + (Ai + Bi)Ci-1

令 Gi = AiBi 所以 Ci = Gi + Pi Ci-1

本地进位, 本地进位,绝对进位

进位产生函数

Pi = Ai + Bi = Ai + Bi = Ai + Bi

进位传递函数 进位条件) (进位条件)

条件进位, 条件进位,传递进位

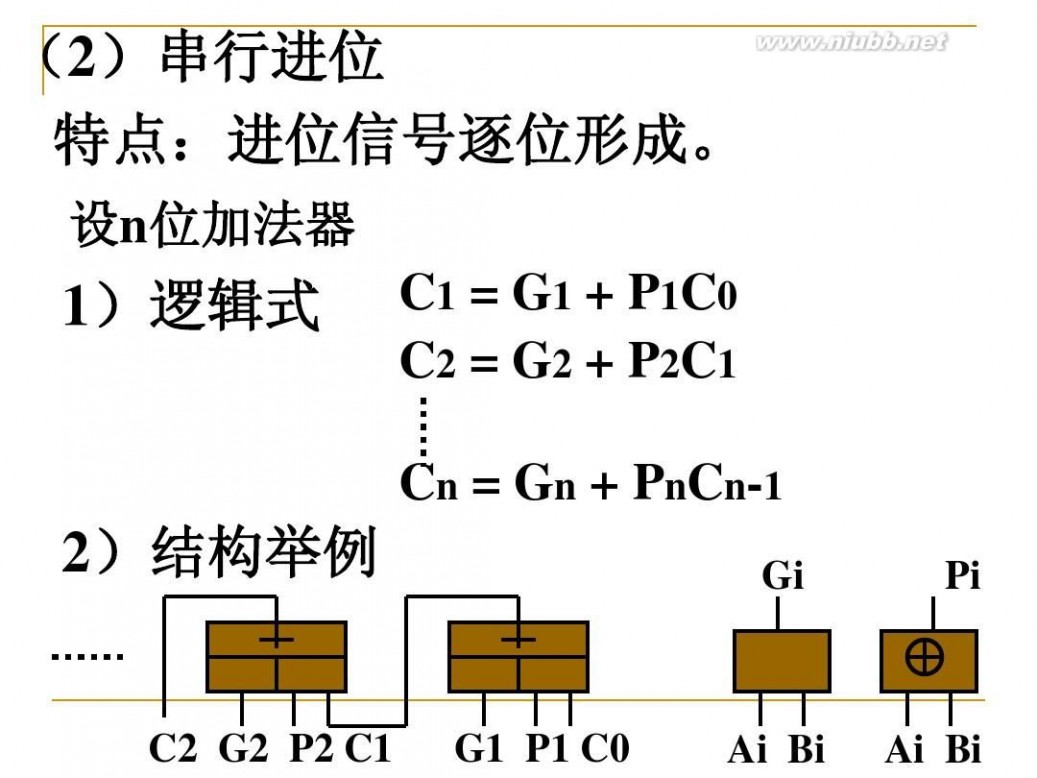

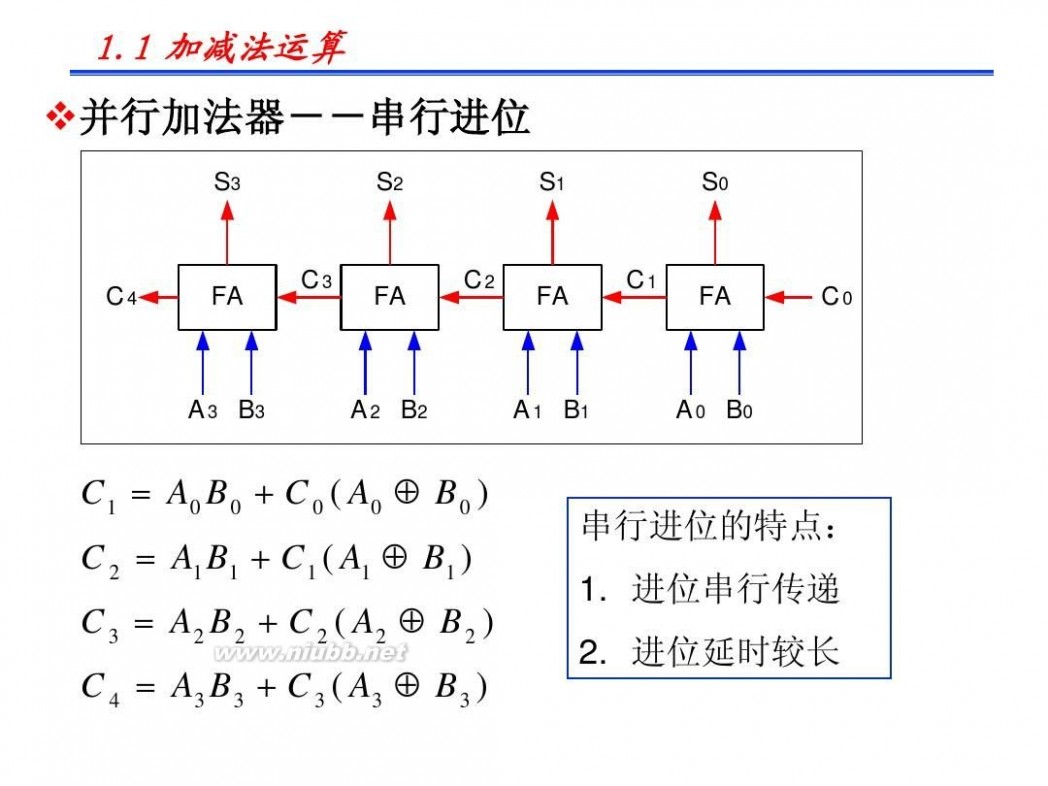

(2)串行进位 ) 特点:进位信号逐位形成. 特点:进位信号逐位形成.

设n位加法器 位加法器

1)逻辑式 )

C1 = G1 + P1C0 C2 = G2 + P2C1 Cn = Gn + PnCn-1

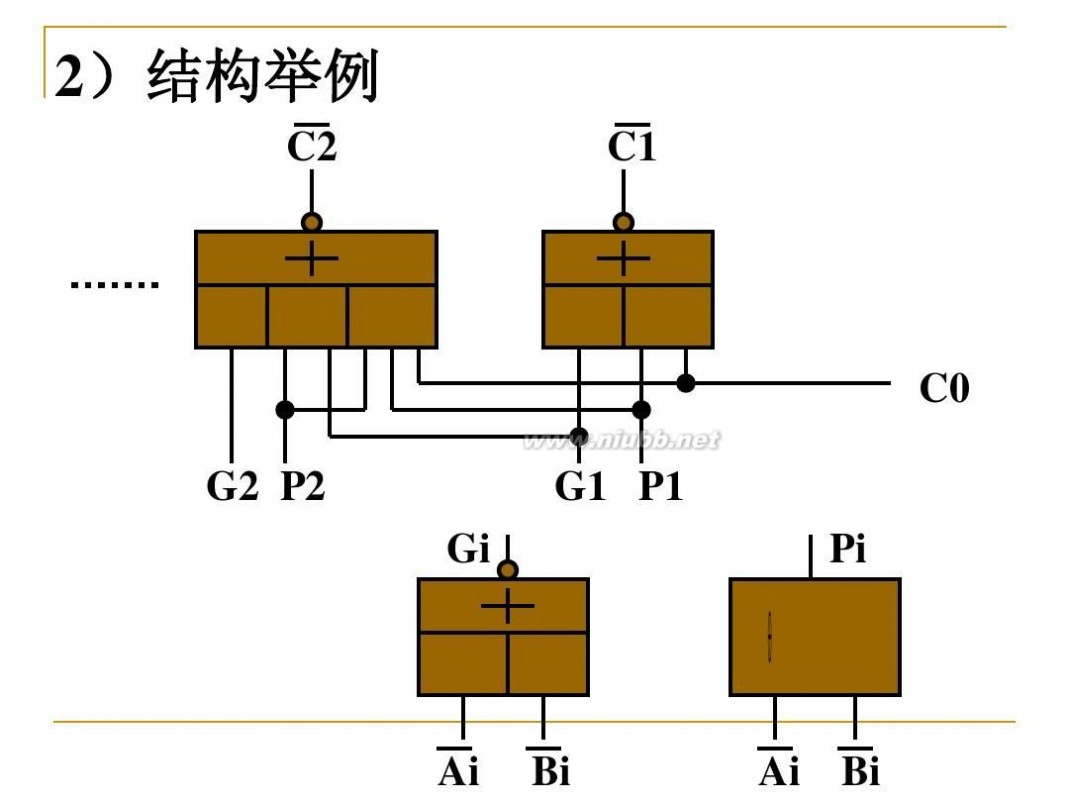

2)结构举例 )

Gi

Pi

C2 G2 P2 C1

G1 P1 C0

Ai Bi

Ai Bi

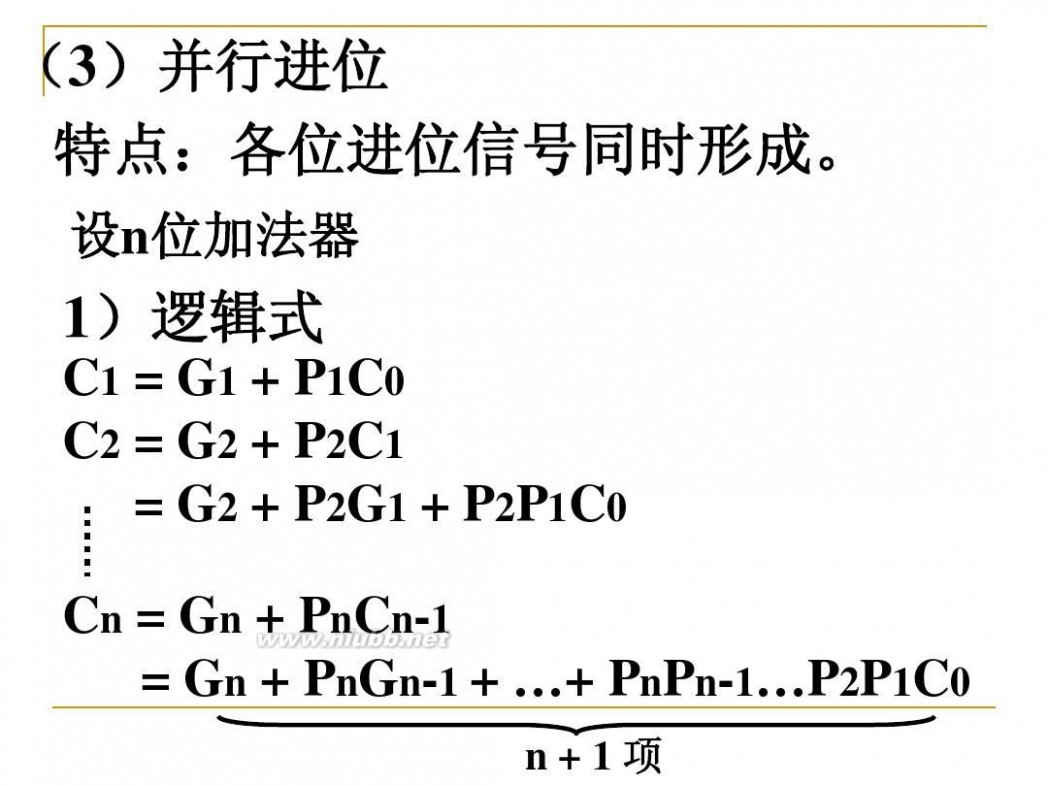

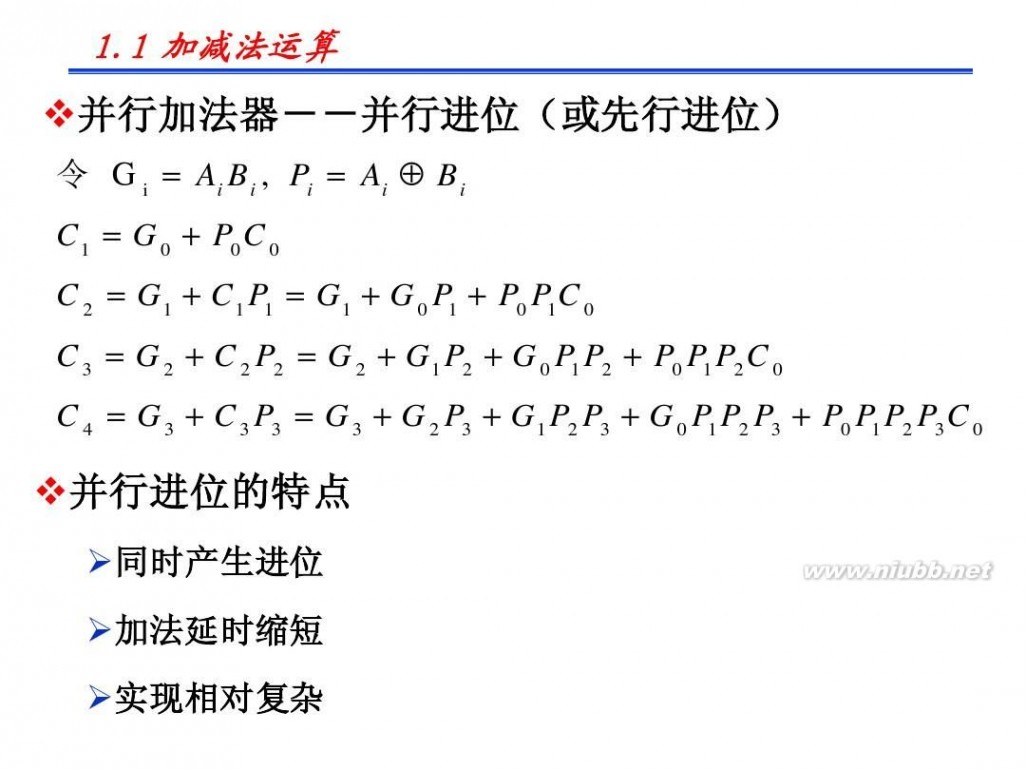

(3)并行进位 ) 特点:各位进位信号同时形成. 特点:各位进位信号同时形成.

设n位加法器 位加法器

1)逻辑式 )

C1 = G1 + P1C0 C2 = G2 + P2C1 = G2 + P2G1 + P2P1C0 Cn = Gn + PnCn-1 = Gn + PnGn-1 + …+ PnPn-1…P2P1C0

n+1项

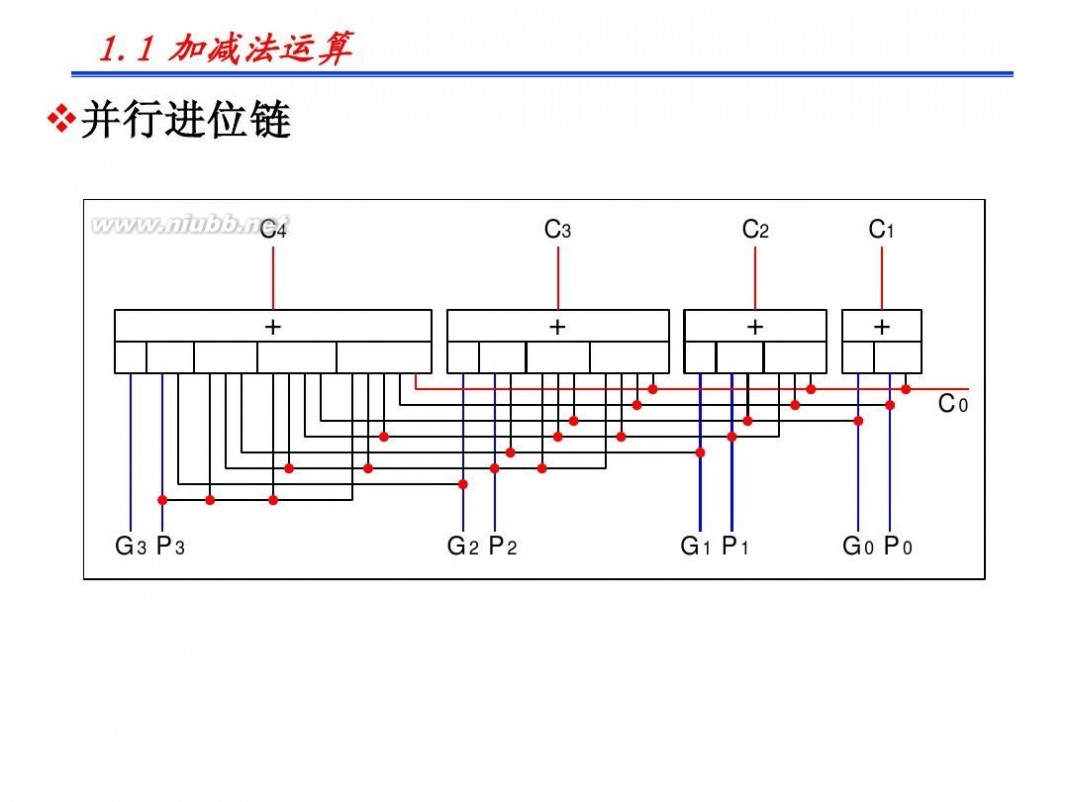

2)结构举例 )

C2 C1

C0 G2 P2 Gi G1 P1 Pi

⊕

Ai Bi Ai Bi

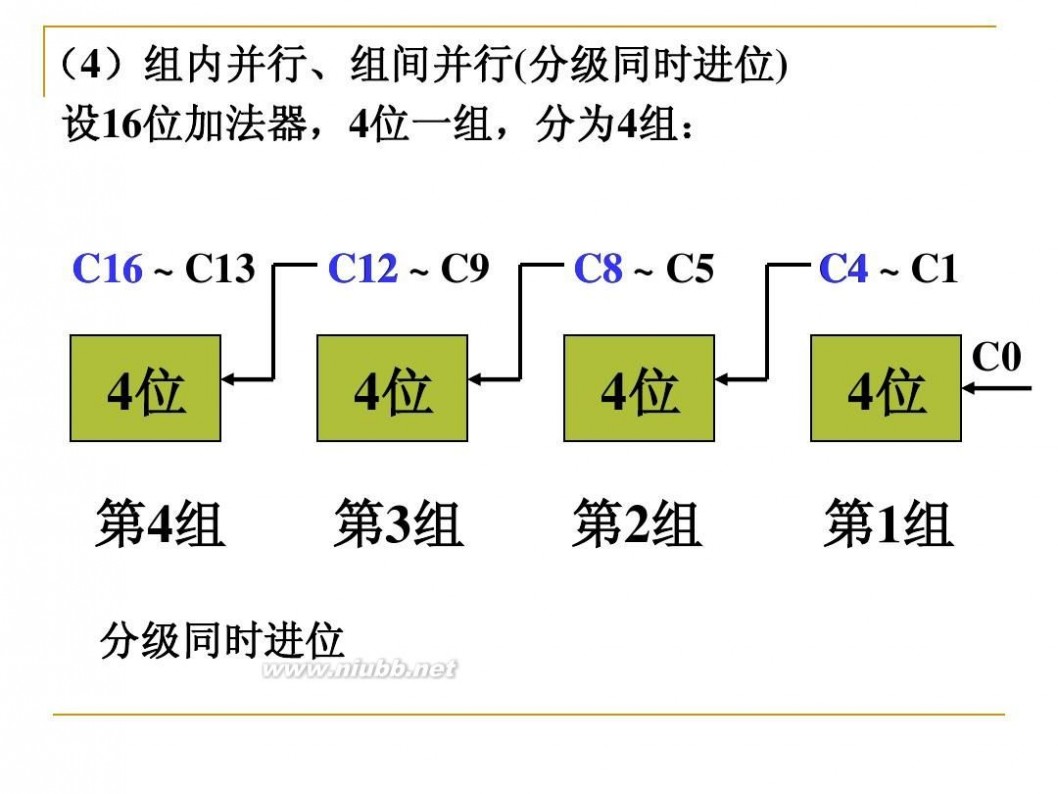

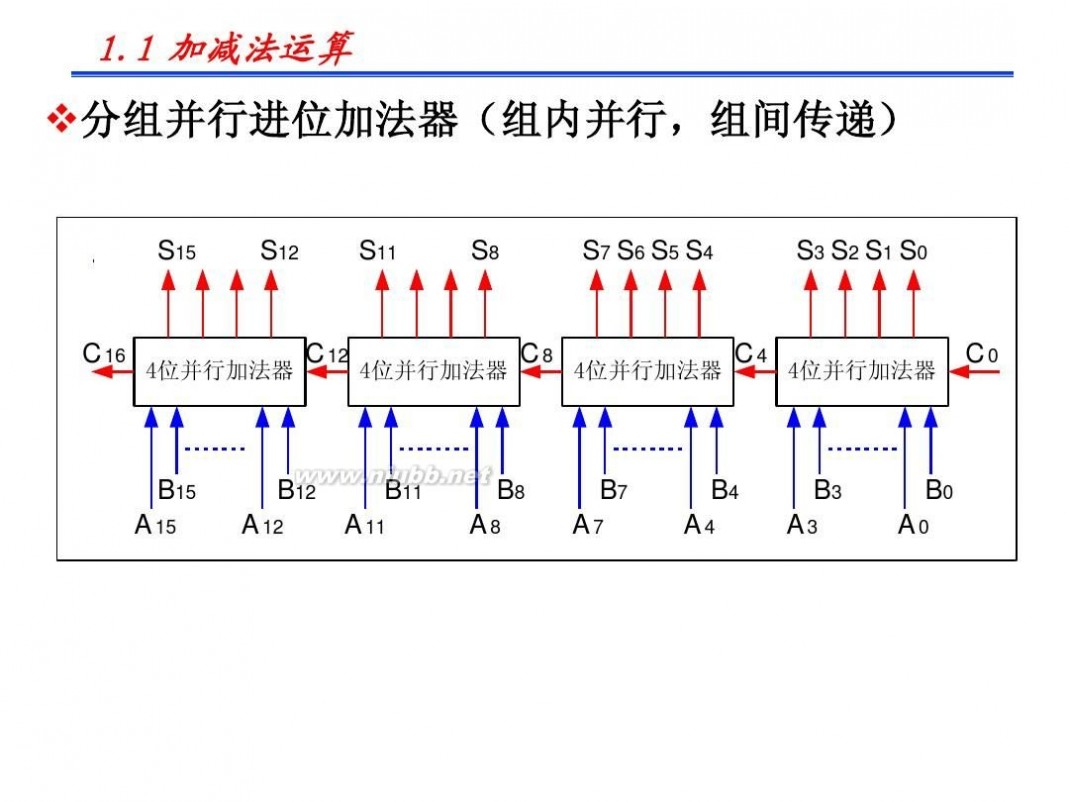

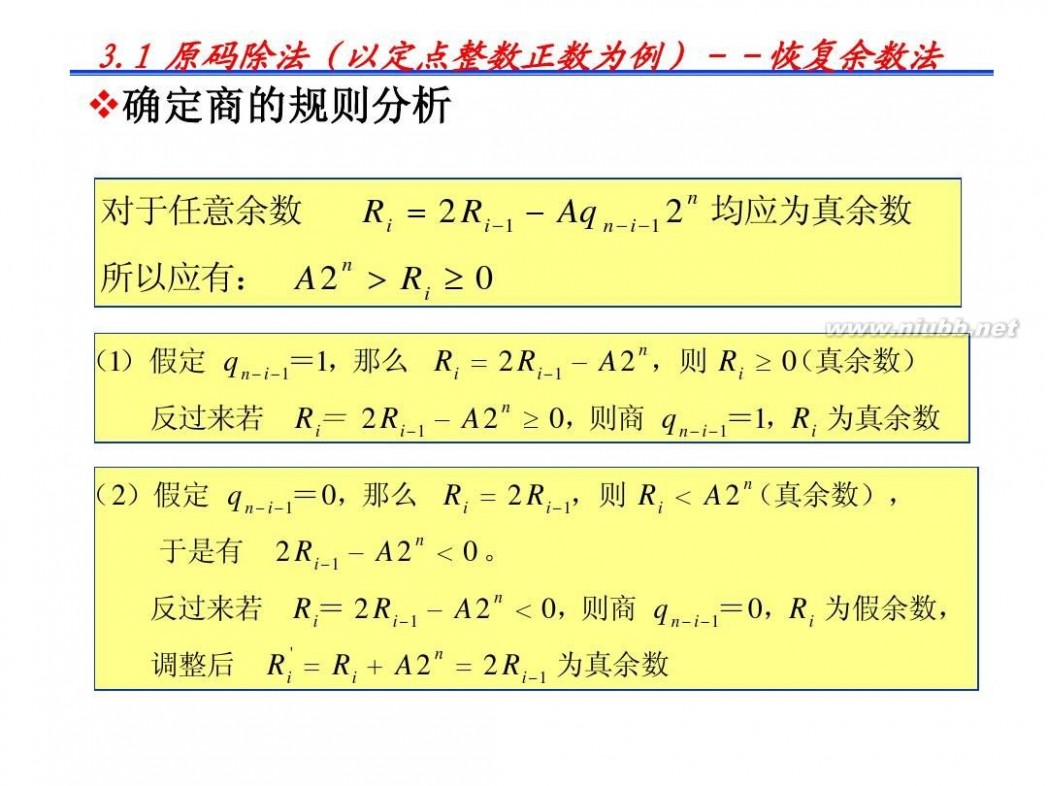

分级同时进位) (4)组内并行,组间并行 分级同时进位 )组内并行,组间并行(分级同时进位 位加法器, 位一组 分为4组 位一组, 设16位加法器,4位一组,分为 组: 位加法器

C16 ~ C13

C12 ~ C9

C8 ~ C5

C4 ~ C1

4位 位 第4组 组

4位 位 第3组 组

4位 位 第2组 组

4位 位 第1组 组

C0

分级同时进位

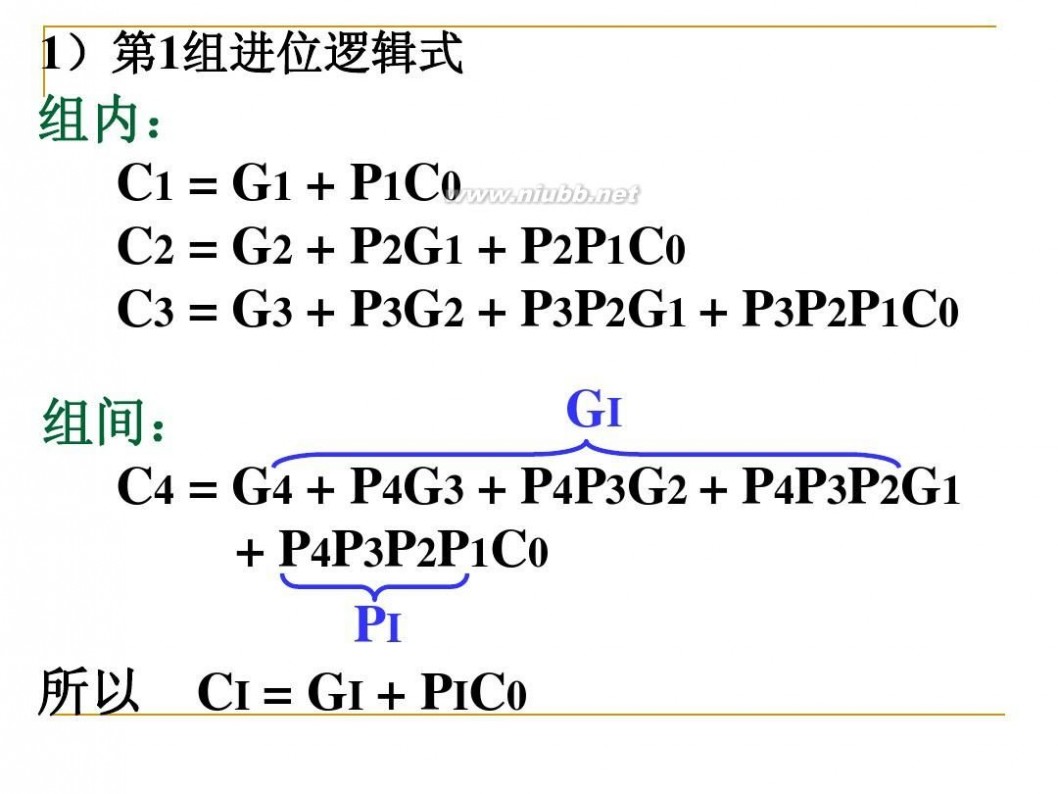

1)第1组进位逻辑式 ) 组进位逻辑式

组内: 组内: C1 = G1 + P1C0 C2 = G2 + P2G1 + P2P1C0 C3 = G3 + P3G2 + P3P2G1 + P3P2P1C0 GI 组间: 组间: C4 = G4 + P4G3 + P4P3G2 + P4P3P2G1 + P4P3P2P1C0 PI 所以 CI = GI + PIC0

2)第2组进位逻辑式 ) 组进位逻辑式

组内: 组内: C5 = G5 + P5CI C6 = G6 + P6G5 + P6P5CI C7 = G7 + P7G6 + P7P6G5 + P7P6P5CI

GⅡ 组间: 组间: C8 = G8 + P8G7 + P8P7G6 + P8P7P6G5 + P8P7P6P5CI PⅡ

所以 CⅡ = GⅡ + PⅡCI

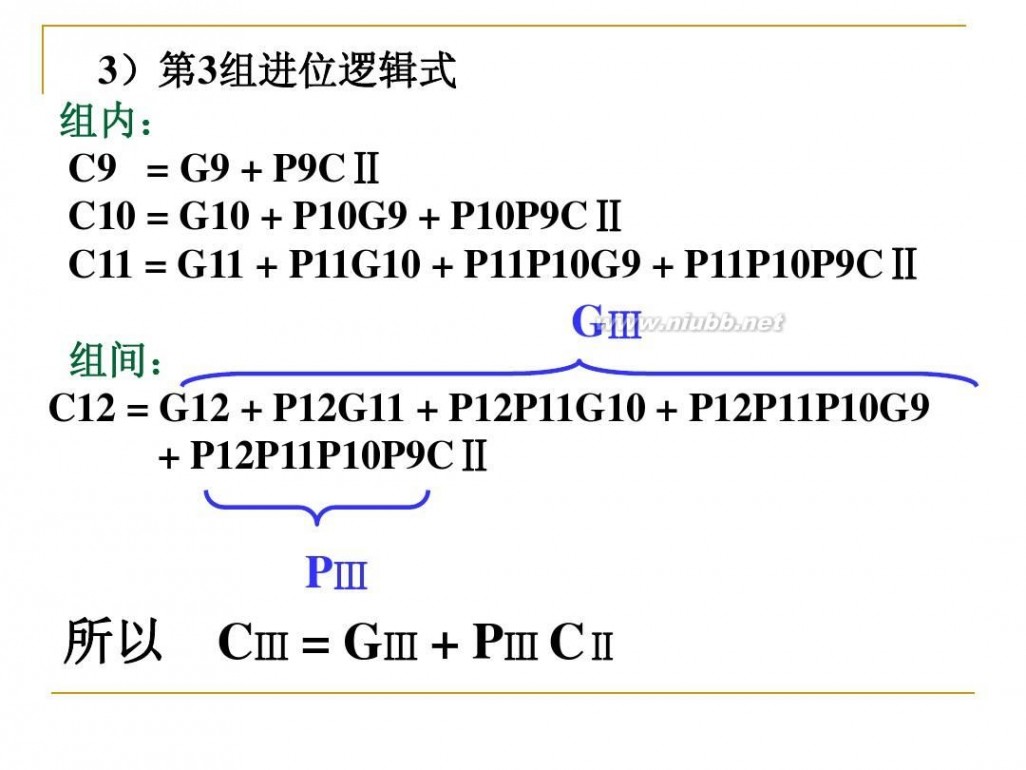

3)第3组进位逻辑式 ) 组进位逻辑式 组内: 组内: C9 = G9 + P9CⅡ Ⅱ C10 = G10 + P10G9 + P10P9CⅡ Ⅱ C11 = G11 + P11G10 + P11P10G9 + P11P10P9CⅡ Ⅱ 组间: 组间: C12 = G12 + P12G11 + P12P11G10 + P12P11P10G9 + P12P11P10P9CⅡ Ⅱ

GⅢ

PⅢ

所以 CⅢ = GⅢ + PⅢ CⅡ

4)第4组进位逻辑式 ) 组进位逻辑式 组内: 组内: C13 = G13 + P13CⅢ Ⅲ C14 = G14 + P14G13 + P14P13CⅢ Ⅲ C15 = G15 + P15G14 + P15P14G13 + P15P14P13CⅢ Ⅲ 组间: 组间: C16 = G16 + P16G15 + P16P15G14 + P16P15P14G13 + P16P15P14P13CⅢ Ⅲ

GⅣ

PⅣ

所以 CⅣ = GⅣ + PⅣCⅢ

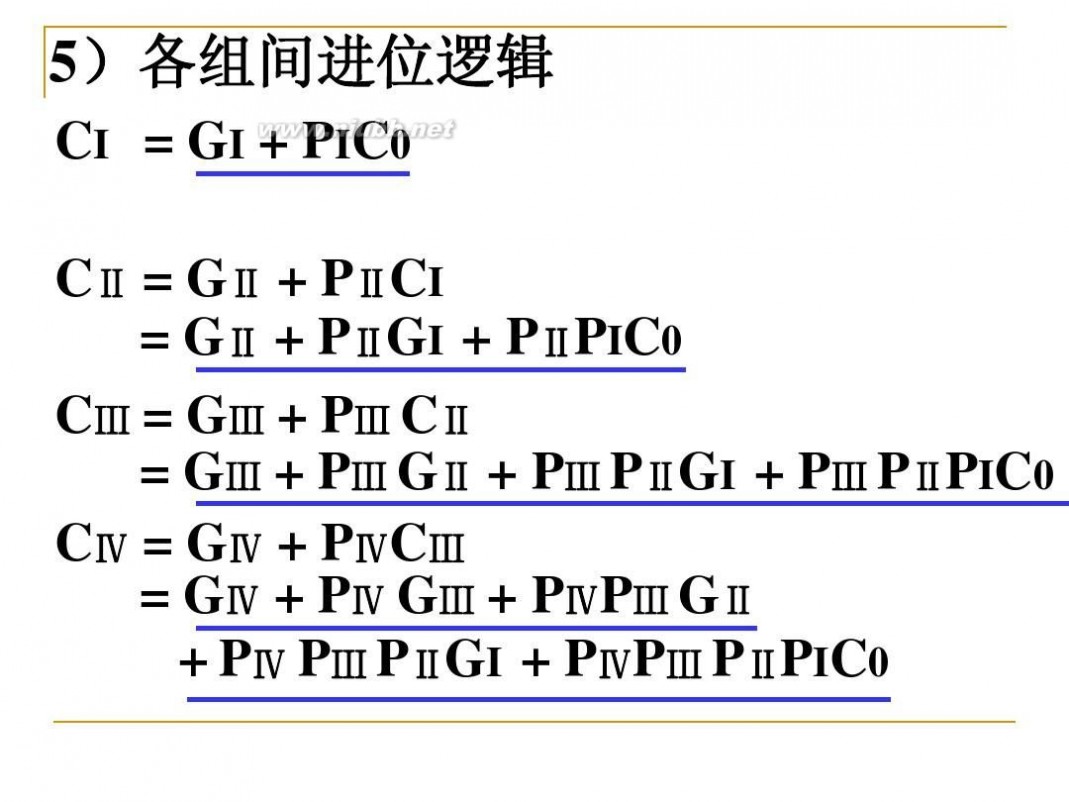

5)各组间进位逻辑 )

CI = GI + PIC0 CⅡ = GⅡ + PⅡCI = GⅡ + PⅡGI + PⅡPIC0 CⅢ = GⅢ + PⅢ CⅡ = GⅢ + PⅢ GⅡ + PⅢ PⅡGI + PⅢ PⅡPIC0 CⅣ = GⅣ + PⅣCⅢ = GⅣ + PⅣ GⅢ + PⅣPⅢ GⅡ + PⅣ PⅢ PⅡ

GI + PⅣPⅢ PⅡPIC0

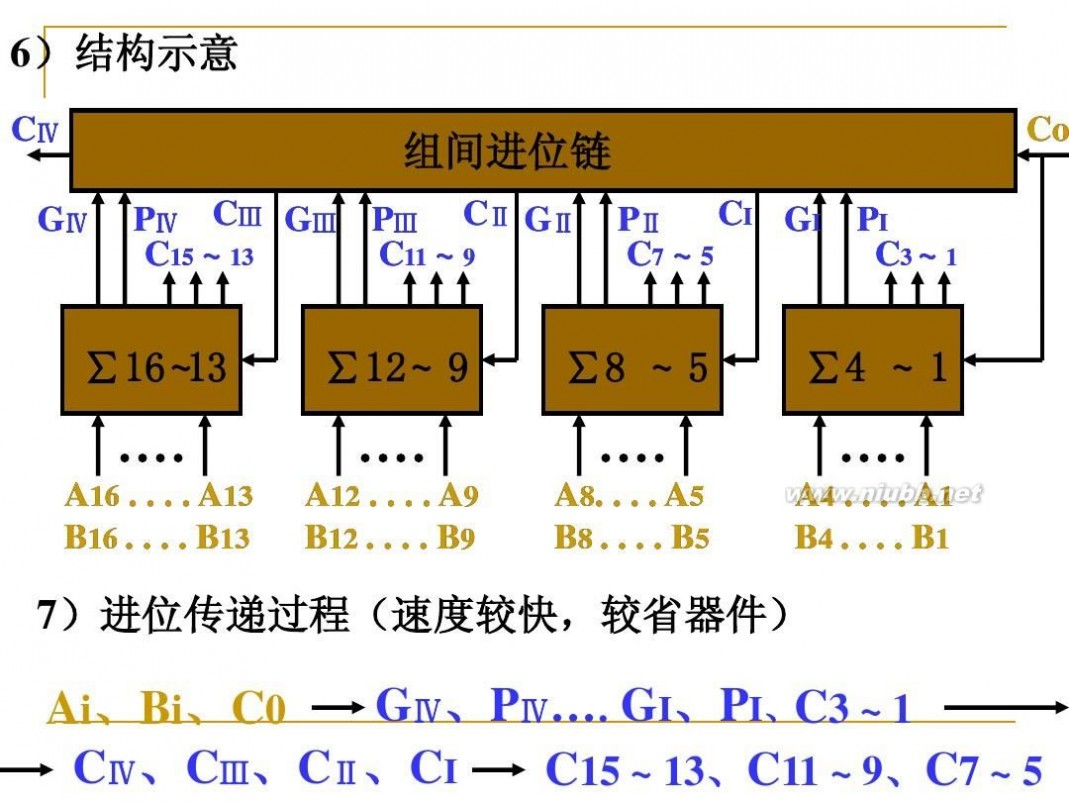

6)结构示意 )

CⅣ GⅣ

组间进位链

PⅣ CⅢ GⅢ PⅢ CⅡ GⅡ C15 ~ 13 C11 ~ 9 CI GI PⅡ C7 ~ 5 PI C3 ~ 1

Co

∑16 ~13

A16 . . . . A13 B16 . . . . B13

∑12 ~ 9

A12 . . . . A9 B12 . . . . B9

∑8 ~ 5

A8. . . . A5 B8 . . . . B5

∑4 ~ 1

A4 . . . . A1 B4 . . . . B1

7)进位传递过程(速度较快,较省器件) )进位传递过程(速度较快,较省器件)

GⅣ,PⅣ….GI,PI,C3 ~ 1 . , Ai,Bi,C0 CⅣ , CⅢ , CⅡ , CI C15 ~ 13,C11 ~ 9,C7 ~ 5 , ,

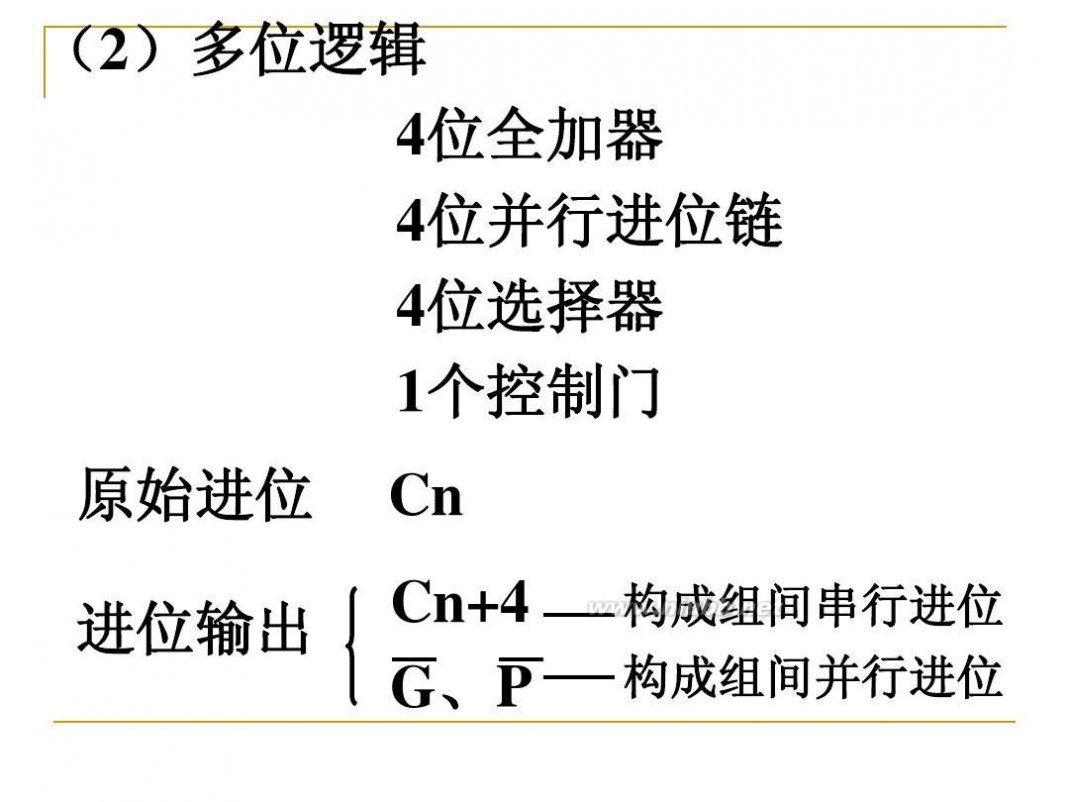

(2)多位逻辑 ) 4位全加器 位全加器 4位并行进位链 位并行进位链 4位选择器 位选择器 1个控制门 个控制门 原始进位 进位输出 Cn Cn+4 G,P ,

构成组间串行进位 构成组间并行进位

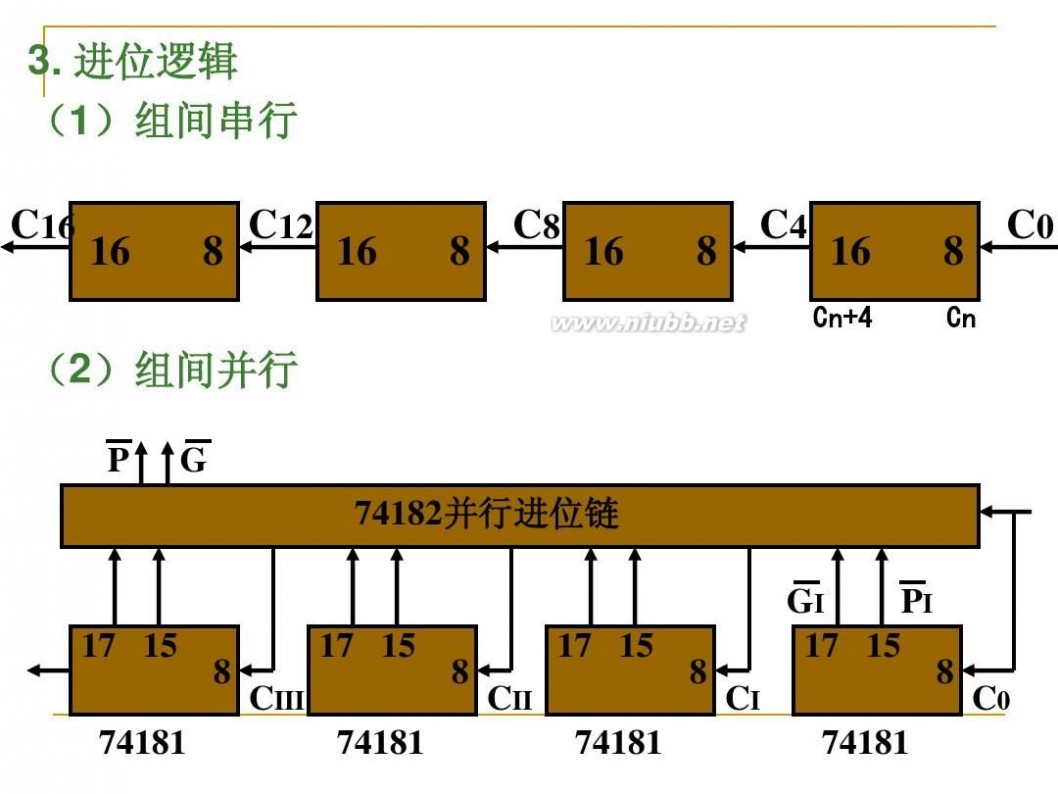

3. 进位逻辑 (1)组间串行 ) C16 16 8 C12 16 8 C8 16 8 C4 16

Cn+4

8

Cn

C0

(2)组间并行 )

P G 74182并行进位链 并行进位链 GI PI 17 15 CI 74181

17 15 74181

8

17 15 CIII 74181

8

17 15 CII 74181

8

8

C0

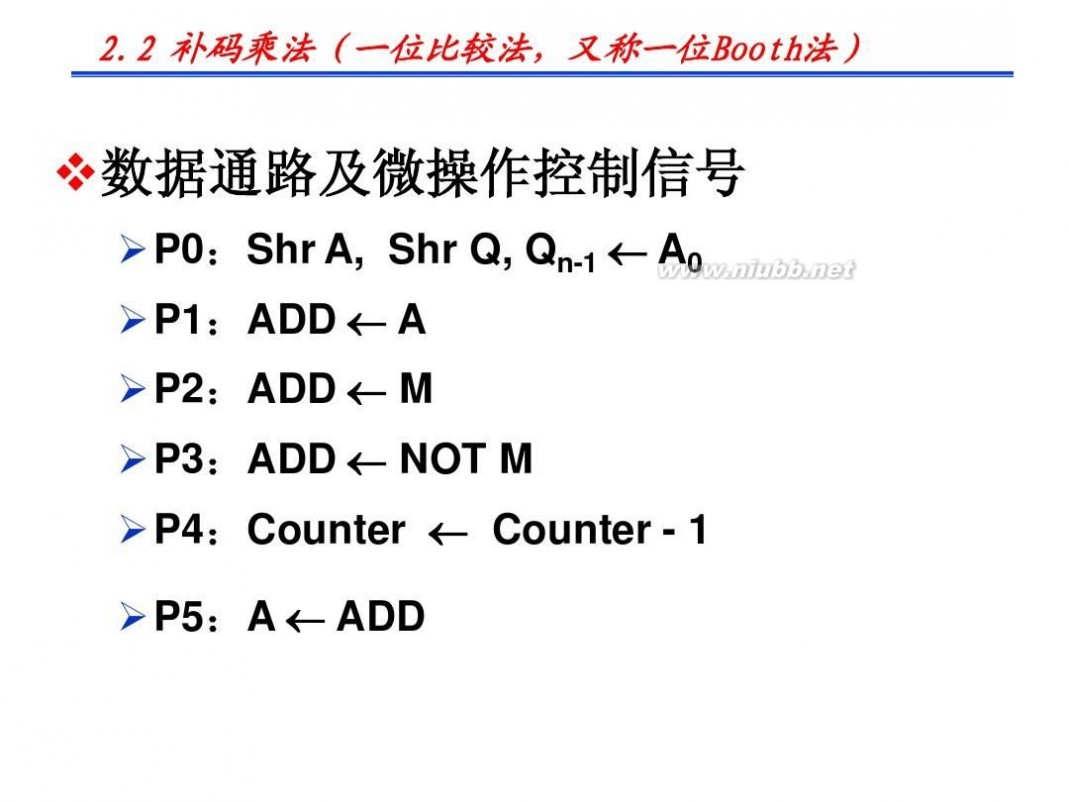

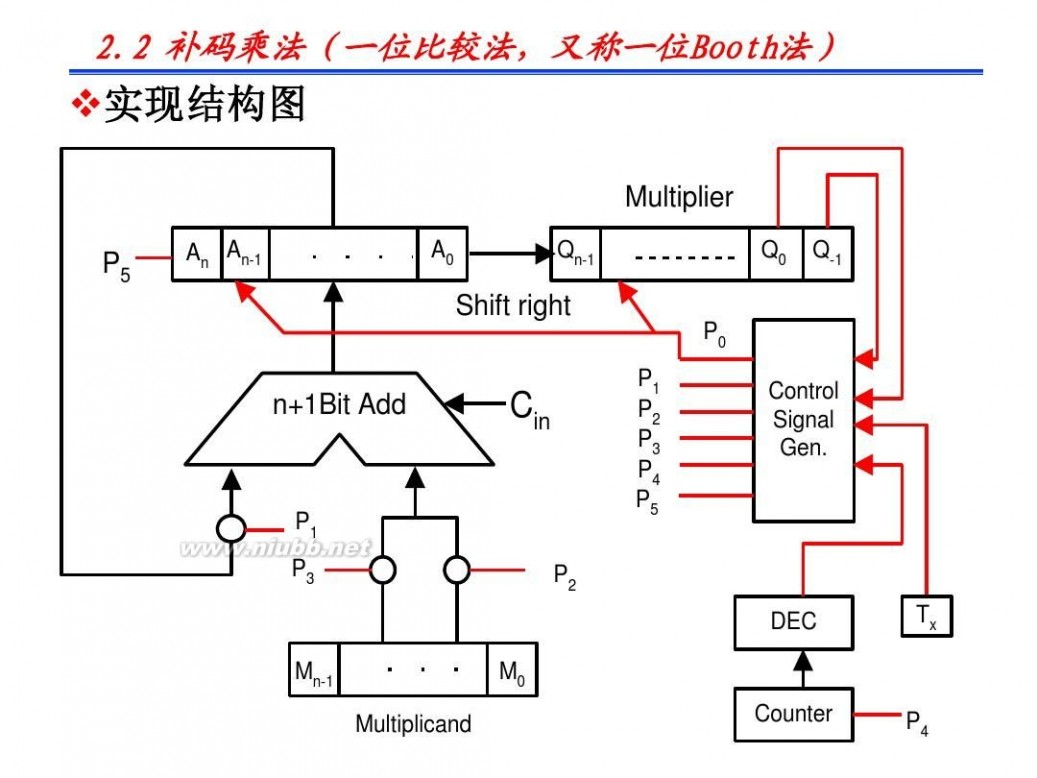

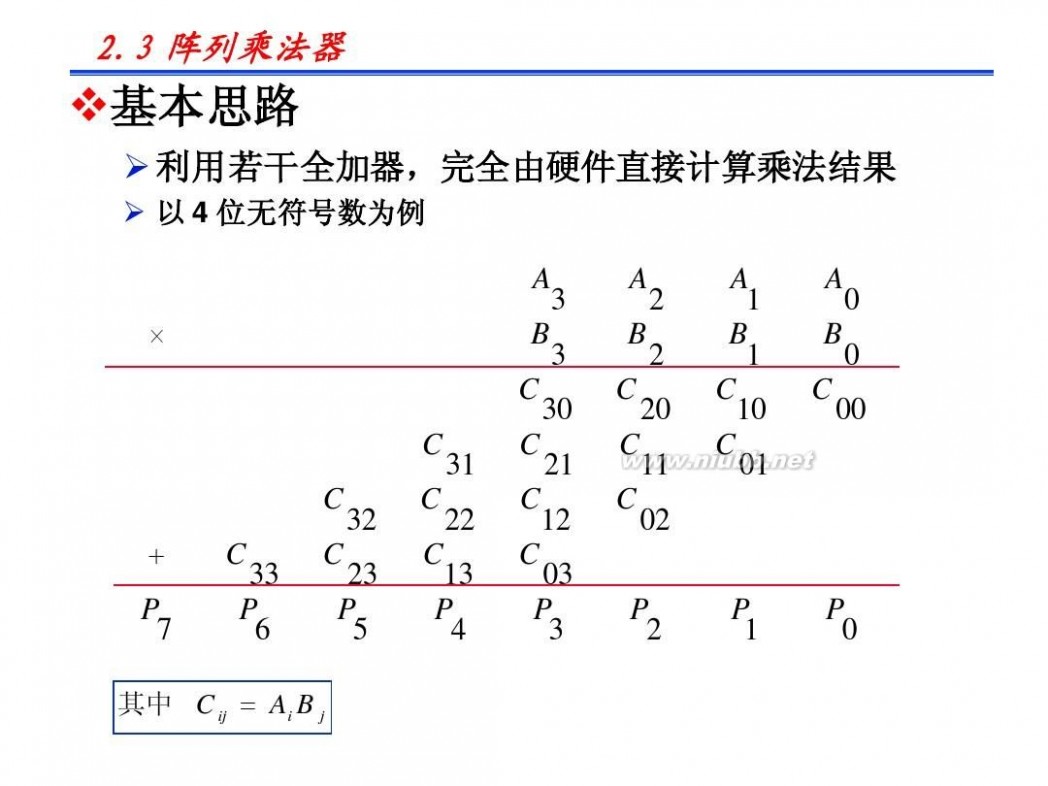

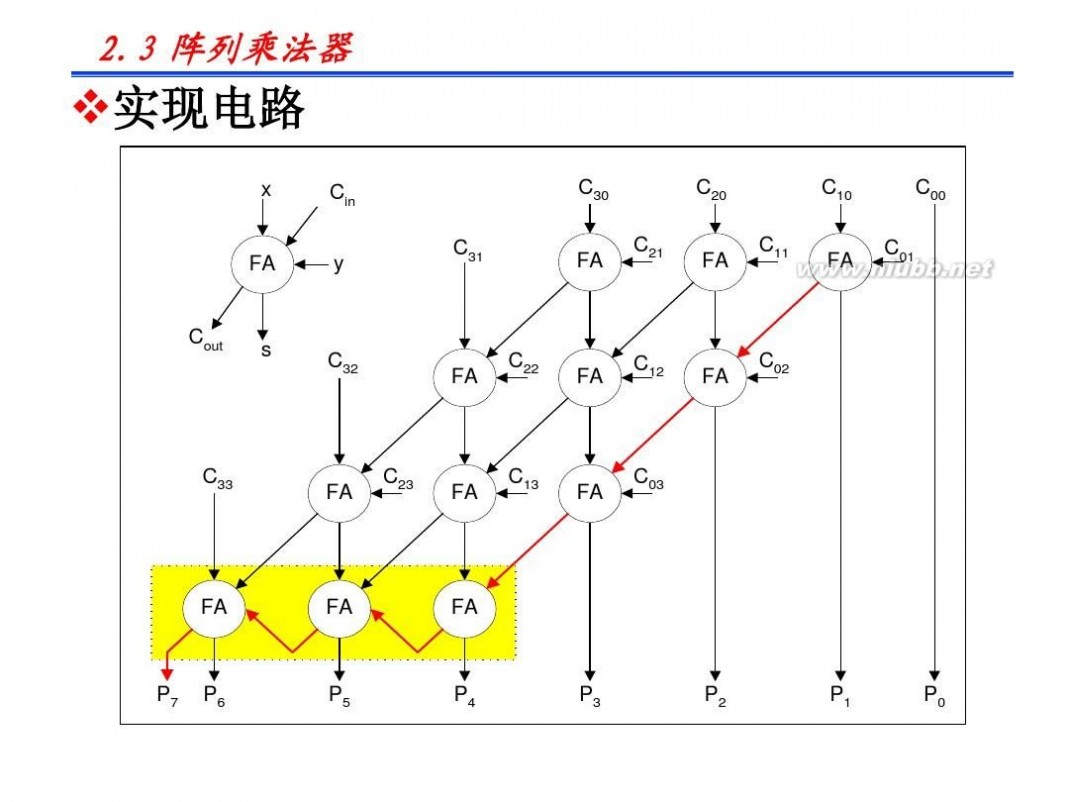

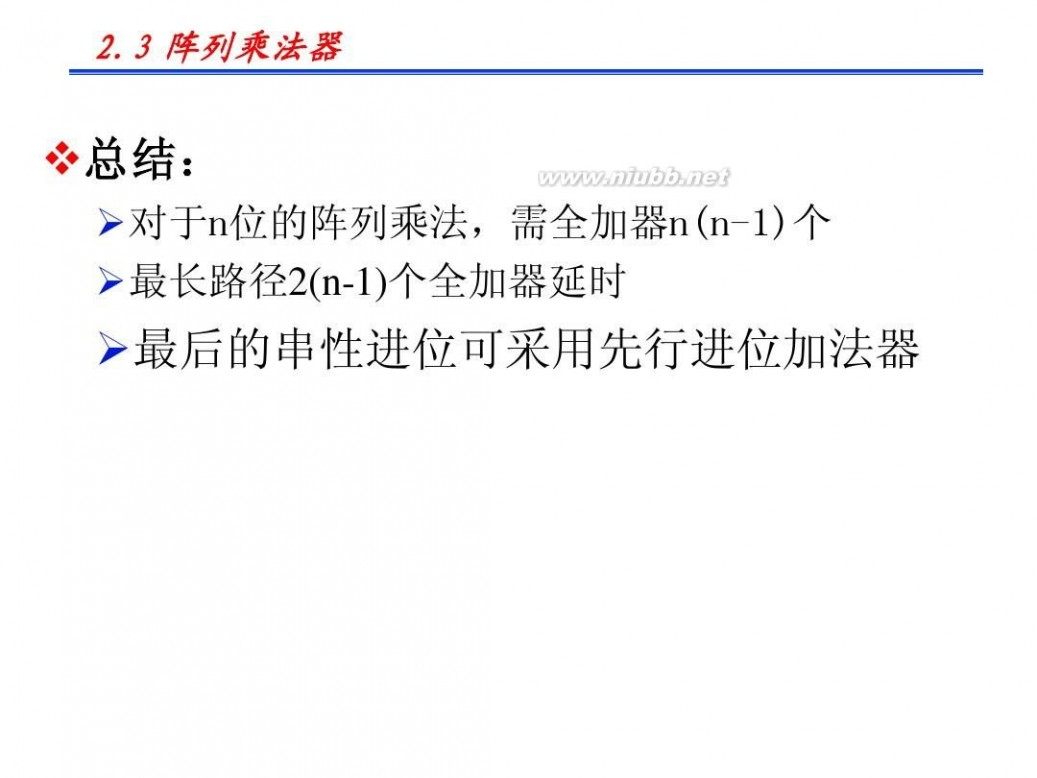

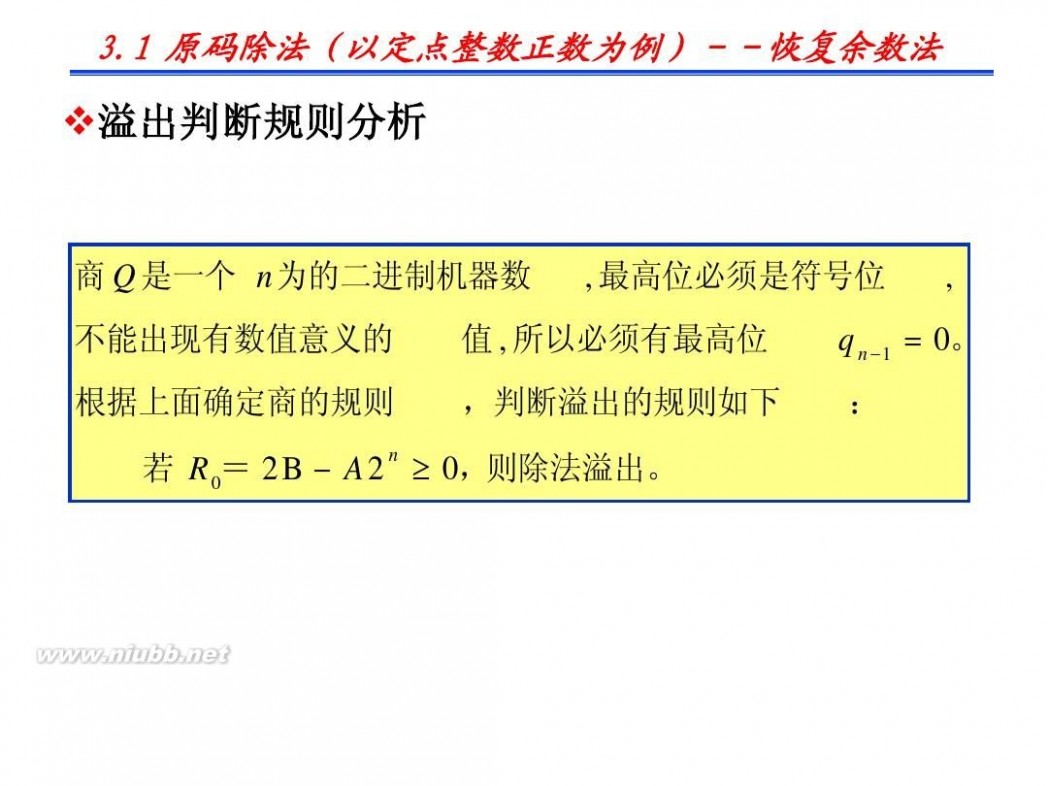

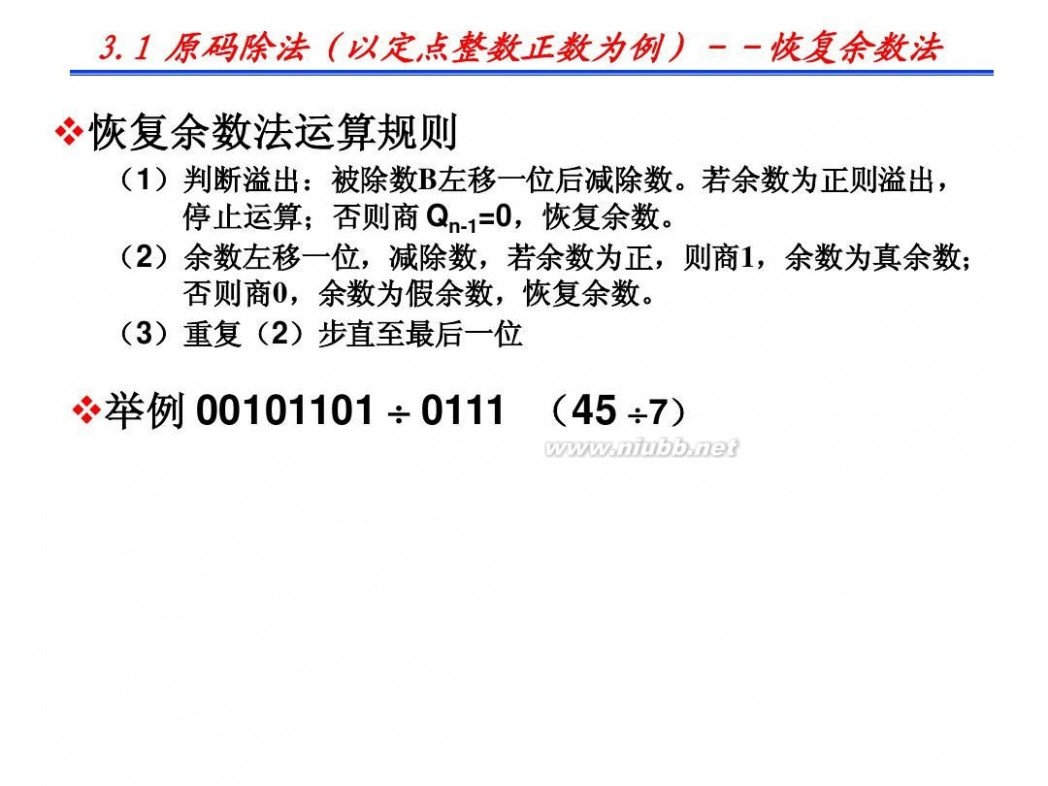

三 : 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

61阅读提醒您本文地址:

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

61阅读提醒您本文地址:

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

booth算法 计算机组成原理CPU运算方法(Part4)

61阅读提醒您本文地址:

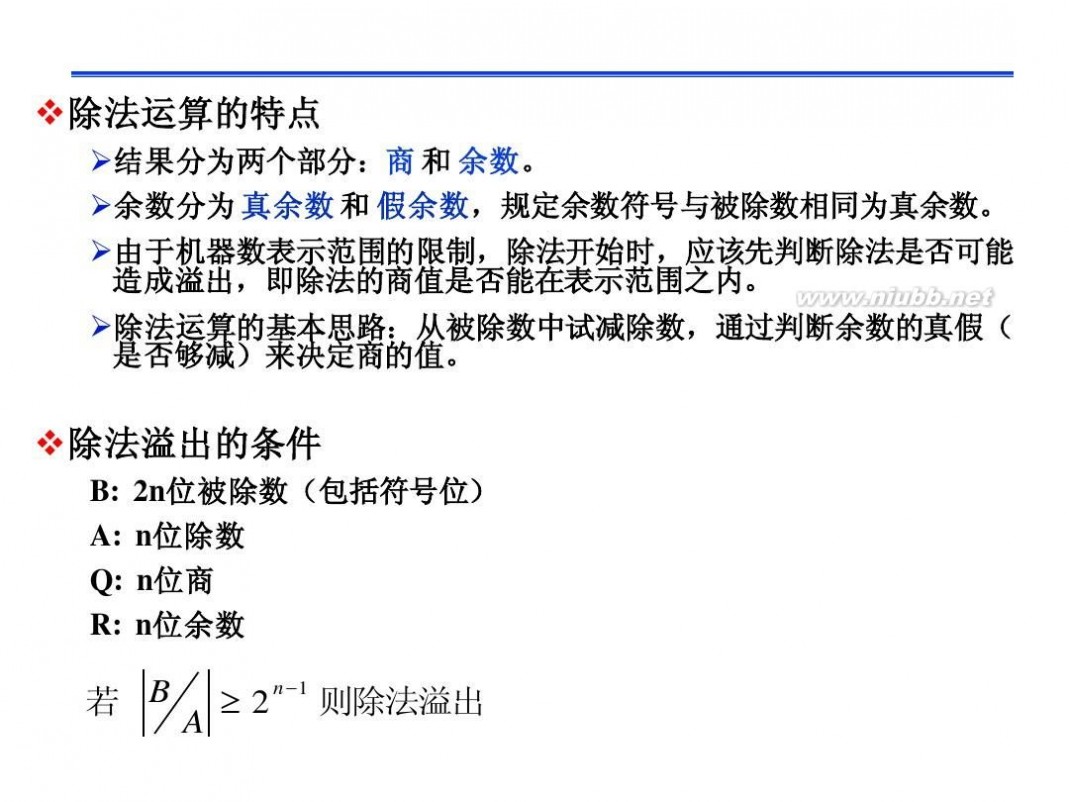

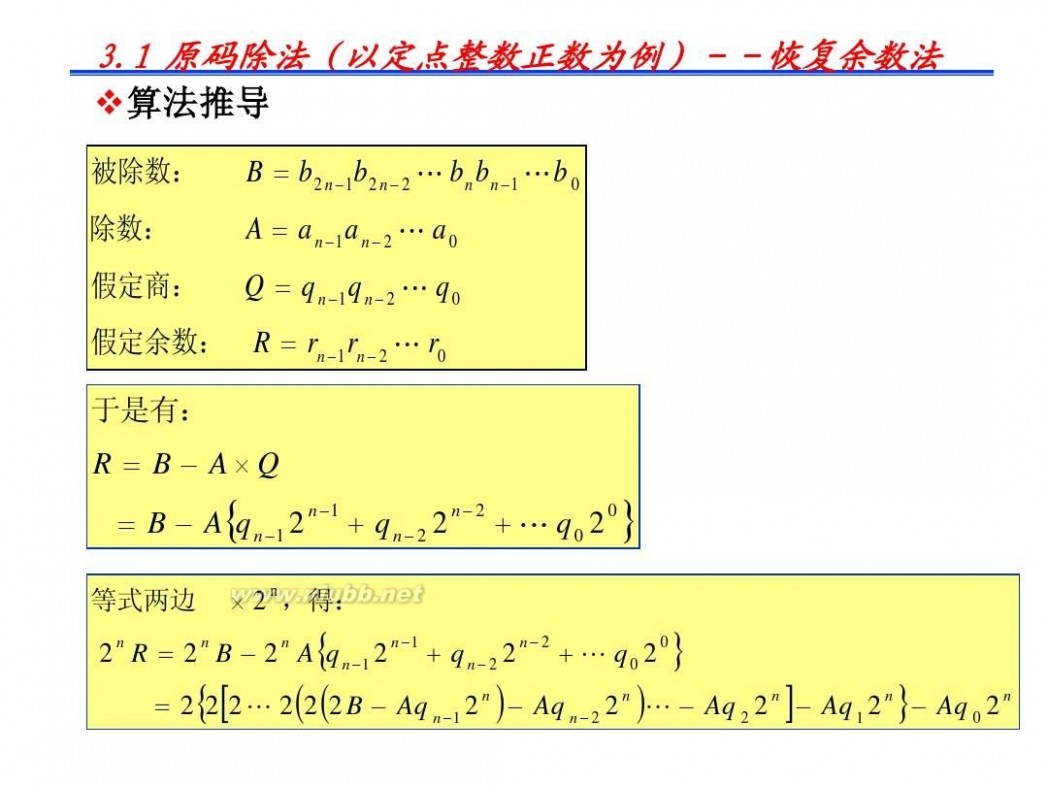

四 : 计算机组成原理79

习题1.1

1.1.1 超级计算机是用于运行大规模问题,并通常通过网络访问的计算机。 1.1.2 petabyte是10或2字节。

1.1.3 服务器是由成百上千处理器和若干terabyte级内存组成的计算机。 1.1.4 虚拟世界是目前尚为科学幻想的应用,但是很有可能即将成为现实。 1.1.5 RAM是1种称为随机访问内存的内存。 1.1.6 CPU是1种称为中央处理器的计算机部件。 1.1.7 数据中心是上千个处理器形成的大集群。

1.1.8 多核处理器是在同1个芯片中含有几个处理器的微处理器。

1.1.9 低端服务器是没有显示器和键盘的桌面计算机,通常通过网络访问。

1.1.10 嵌入式计算机是当季最大的1类计算机,运行1个应用或一组相关的应用。 1.1.11 VHDL是用于描述硬件部件的特殊语言。

1.1.12 桌面计算机是对单用户以低成本提供高性能的个人计算机。 1.1.13 编译程序讲高级语言语句翻译成汇编程序的程序。 1.1.14 汇编程序将符号指令翻译成二进制指令的程序。 1.1.15 Cobol是商业数据处理用的高级语言。

1.1.16 机器语言是处理器能够理解的二进制语言。 1.1.17 指令是处理器能够理解的命令。 1.1.18 Fortran是科学计算用的高级语言。 1.1.19 汇编语言是机器指令的符号语言。

1.1.20 操作系统是用户程序和硬件之间的接口,能提供许多服务和监视功能。 1.1.21 应用软件是用户开发的软件/程序。 1.1.22 位是二进制位(值为0或1)。

1.1.23 系统软件是应用软件和硬件之间的软件层,包括操作系统和编译程序。 1.1.24 C语言是用于编写应用程序和系统软件的高级语言。

1.1.25 高级语言是由字和代数符号组成的可移值语言,在计算机中运行前必须翻译成汇编语言。

1.1.26 terabyte是10或2字节。

1215

50

40

习题1.2

1.2.11个彩色显示器中的每个像素由3种基本(红、绿、蓝)构成,每种基色用8位表示,分辨率为1280×800像素。请问为了保存一帧图像需要多大的缓存(以字节计算)? 解:8bits× 3=24bits/pixel=4bytes/pixel

1280×800pixel=1024000pixel

1024000pixel × 4bytes/pixel=4096000pixel(接近4M bytes)

1.2.2如果一台计算机有1个2GB的主存,并且该主存的没有存储其他信息,他最多可保存多少帧图像?

解:2GB=2048Mbytes

Frames=2048Mbytes/4Mbytes=512frames

1.2.3如果一台计算机连接到1Gbps以太网上,发送256KB的文件需要多长的时间?

解:从1 Gbps network 可以==>

1 Gbps/per second = 125 Mbytes/second.

文件大小是 256 Kbytes = 0.256 Mbytes.

所以发送文件的时间是: 0.256 Mbytes = 0.256/125 = 2.048 ms.

1.2.4假定cache比DRAM快10倍,DRAM比磁盘快10000倍,闪存比磁盘快1000倍。如果从cache读取1个文件需要2微秒,请问从DRAM、磁盘和闪存读取需要多长时间? 解: 2 ms from cache ==> 20 ms from DRAM.

20 ms from DRAM ==> 2 seconds from magnetic disk.

20 ms from DRAM ==> 2 ms from ?ash memory.

习题1.3

1..3.1解:由经典的CPU性能公式:CPU时间=指令数×CPI/时钟频率 可以推出:

P1、P2、P33个处理器在执行相同的指令集的情况下,所用时间最少的性能最高。所以只需要算出时间的倒数,最高的性能最好! P1的性能=(2.0×10)/1.5=1.33×10 P2的性能=(1.5×10)/1.0=1.5×10 P3的性能=(3.0×10)/2.5=1.2×10

所以P2的性能最好!

1.3.2如果每个处理器执行1个程序都要花费10秒钟的时间,求他们的时钟周期和指令集? 解:

时钟周期=程序执行时间×时钟频率 P1时钟周期=10×(2.0×10)=2.0×10S P2时钟周期=10×(1.5×10)=1.5×10S P3时钟周期=10×(3.0×10)=3.0×10S

时钟周期=程序的指令数×CPI,所以程序的指令数=时钟周期/CPI P1的指令数=(2.0×10S)/1.5=1.33×10 P2的指令数=(1.5×10S)/1.0=1.5×10 P3的指令数=(3.0×10S)/2.5=1.2×10

1.3.3我们试图把时间减少30%,但是这会引起CPI增加20%。时钟频率应该是多少才能达到时间减少30%的目的?

解:执行时间减少30%也就是执行时间是7秒,CPI增加20%后是CPI1=1.8,CPI2=1.2,CPI3=3。

时钟频率=指令数×CPI/执行时间,所以 P1的时钟频率=1.33×10×1.8/7=3.42GHz

1010

10

10

10

10

10

9

10

9

10

9

10

9

9

9

9

9

9

P2的时钟频率=1.5×10×1.2/7=2.57GHz P3的时钟频率=1.2×10×3.0/7=5.14GHz

1.3.4解:

IPC=1/CPI , 时钟周期=程序的指令数×CPI , 所以可以推出 IPC1=1.42 IPC2=2 IPC3=3.33 1.3.5解:

P1执行时间/P2执行时间= 7/10 = 0.7

所以 P2的新时钟频率 = P2的之前的时钟频率/0.7 = 1.5 GHz/0.7 = 2.14 GHz才能将其执行时间减少到和P1一样。 1.3.6解:

P3的执行时间/P2的执行时间 = 9/10 = 0.9

所以P2的新的指令数=P2的之前的指令数 ×0.9 = 3.0 ×10×0.9=2.7×10才能将其执行时间减少到和P3一样。

10

10

10

10

习题1.4

1.4.1给定1个程序,有106条指令,按照比例分为4类:A、10% B、20% C、50% D、20%,哪种实现方式更快? 解:

P2实现方式更快:

4类:A、10 B、2×10 C、5×10 D、2×10 CPU时间=指令数×CPI/时钟频率

P1所用时间:0.66×10+2.66×10+10×10+5.33×10=18.65×10 P2所用时间:10+2×10+5×10+3×10=11×10 1.4.2每中实现方式总的CPI

解: CPI=执行时间×时钟频率/指令数 可以推出: CPI1=2.79

CPI2=2.2

1.4.32种情况下的时钟周期各式多少? 解:时钟周期数=指令数×CPI

P1的时钟周期=1×10+2×10×2+3×10×5+4×10×2=28×10 P2的时钟周期=2×10+2×10×2+5×10×2+2×10×3=22×10

1.4.4假定算术指令用时个周期,存储和取数用时各五个周期,分支用时2周期。该程序在2GHz的CPU上运行,执行时间是多少?

5

5

5

5

5

5

5

5

5

5

?4

?4

?4

?4

?4

?4

?4

?4

?4

?4

5

5

5

5

解:(500 × 1 + 50 × 5 + 100 × 5 + 50 × 2) × 0.5 × 10= 675 ns 1.4.5求该程序的CPI是多少?

解:CPI = 675 × 10× 2 ×10/700 = 1.92

1.4.6如果取数指令减少一半,则增速和CPI分别是多少? 解:

时钟周期 = (500 × 1 + 50 × 5 + 50 × 5 + 50 × 2) × 0.5 × 10= 550 ns 增速= 675 ns/550 ns = 1.22

CPI = 550 × 10 × 2 ×10/700 = 1.57

?9

9

?9

?9

9

?9

习题1.6

1.6.1同样的程序,采用两个不同的编译程序A、B,在给定处理器时间周期为1ns时,每个程序的平均CPI?

1.6.2CPI和上题相同,但是编译程序实在两个不同的处理器上运行的。如果这两个处理器额执行时间相同,求运行编译程序A的处理器相对于编译程序B的处理器的时钟快多少? 解:a:0.86

b:1.37

1.6.3假设开发了1种新的编译程序,只用6亿条指令,平均CPI为1.1。求这种新的程序相对于上面2个题中的编译程序A和B的加速比?

解: 1.6.4假定将一台计算机执行任何指令序列所能达到的最快速率定义为峰值性能。求P1,P2

的峰值性能,单位为每秒指令数。 解:

1.6.5如果在某个程序中执行的指令数均等地分布于除A类以外的各类指令,A类指令数是其他类指令数的2倍。求P2比P1块多少? 解:

1.6.6在上题之中,P2的频率为多少时,其性能和P1相同?

习题1.7

1.7.1分别求出相邻2代处理器的时钟频率之比和功耗之比的几何平均值? 解:

1、相邻时钟平均之比的几何平均值:(1.28 × 1.56 × 2.64 × 3.03 × 10.00 × 1.80 × 0.74)/7= 2.15 2、相邻功耗之比的几何平均值: (1.24 × 1.20 × 2.06 × 2.88 × 2.59 × 1.37 × 0.92)/7=1.62 1.7.2分别求出不同两代间的处理器的时钟频率和功耗的相对变化量的最大值? 解:

1、时钟频率的相对变化量的最大值=2000 MHz/200 MHz = 10 2、功耗的相对变化量的最大值= 29.1 W/10.1 W = 2.88

1.7.3分别求出最后一代处理器比第一代处理器在时钟频率和功耗上增长的倍数? 解:

1、时钟频率增长的倍数=2.667 × 10/12.5 ×10 = 212.8 2、功耗上的增长倍数=95 W/3.3 W = 28.78 1.7.4假定静态功耗不计,求平均电容负载? 解:C=P/V ×时钟频率

80286:C = 0.0105 × 10 Pentium Pro(1997): C = 0.0133×10 80386:C = 0.01025×10 80486:C = 0.00784×10 Pentium:C = 0.00612×10

?6?6?6?6

?6

2

9

6

Pentium 4 Willamette: C = 0.0122×10 Pentium 4 Prescott:C = 0.00183×10

?6

?6

?6

Core 2 Ketsfield :C = 0.0294×10

1.7.5相邻哪两代处理器间电压相对变化最大? 解:

3.3/1.75 = 1.78 (Pentium Pro to Pentium 4 Willamette)

1.7.6求从Pentium型号开始的不同代处理器间的电压的几何平均值? 解:

Pentium to Pentium Pro: 3.3/5 = 0.66 Pentium Pro to Pentium 4 Willamette: 1.75/3.3 = 0.53 Pentium 4 Willamette to Pentium 4 Prescott: 1.25/1.75 = 0.71 Pentium 4 Prescott to Core 2: 1.1/1.25 = 0.88 平均值 = 0.68

计算机组成原理79_计算机组成原理

习题1.8

1.8.1如果两版本之间动态功耗减少了10%,求电容负载减少了多少?

解:

版本1功耗= V× 时钟频率 × C 版本2功耗= 0.9×版本1功耗

C2/C1 = 0.9 × 5 × 0.5 × 10/3.3× 1 ×10= 1.03

1.8.2如果电容负载不变,动态功耗减少了多少?

解:

版本2功耗/版本1功耗= V2× 时钟频率2/V1× 时钟频率

版本2功耗/版本1功耗 = 0.87 =>减少了13%

1.8.3假定第2版的电容负载时第1版的80%,如果第2版的动态功耗与第1版相比减少了40%,求第2版的电压?

解:

版本2的功耗= V2×1×10×0.8×C1 = 0.6 × 版本1的功耗

版本1的功耗=5×0.5×10×C1 29292922229

V2=0.36V

1.8.4动态功耗的比例因子是多少?

解:

新的功耗= 1×Cold×Vold/(22?1

42)×时钟频率×2= 以前的功耗 1

2

所以比例因子是1.

1.8.5求单位面积的电容的比例?

解:

1

2?1

2=2 12

1.8.6用1.7题的数据,求下一代双核处理器的电压和时钟频率?

解:

电压V=1.1×1

2?1

4=0.92V

时钟频率=2.667×2=3.771GHz

12

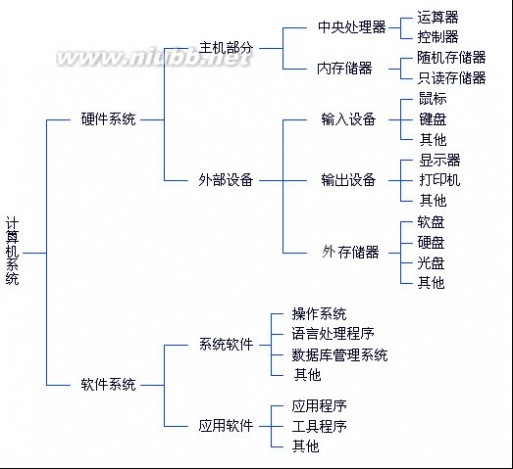

五 : 计算机组成原理

61阅读/ www.61k.net

目录

计算机概述

数据

总线

CPU

存储器

输入/输出设备

计算机的时标系统

计算机概述

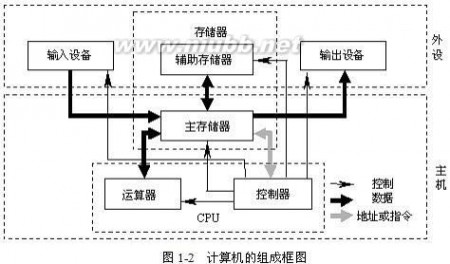

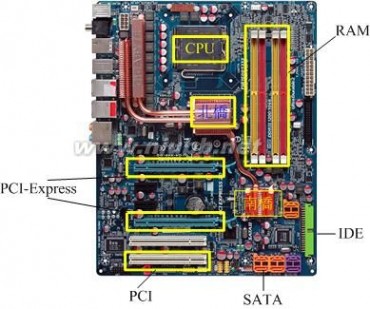

计算机的基本组成:

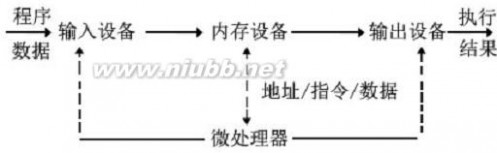

组成的联系:

计算机的工作过程:

冯·诺依曼机制:

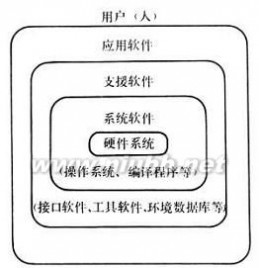

计算机系统的体系结构:

数据概述

数据信息的两种基本方法:

信息的存储单位:

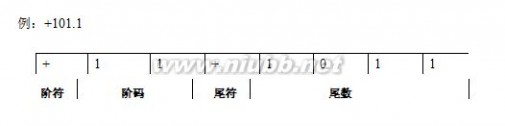

浮点表示法:

公式: N=2^(+-e)*(+-s)

说明:

R进制表示法:

计算机中常用的进制数的表示:

进位制二进制八进制十进制十六进制

规则 逢二进一 逢八进一 逢十进一 逢十六进一

基数 R=2 R=8 R=10 R=16

数码 0、1 0…7 0…9 0…F

权 2^i 8^i 10^i 16^i

形式表示 B Q D H

不同进制之间的转化:

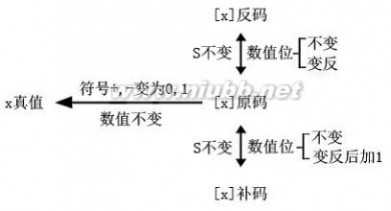

原码,反码,补码,BCD码:

二进制的原码,反码及补码:

原码,反码,补码之间的关系:

BCD码:

(二→十进制) 用思维二进制代码对一位十进制数进行编码

例:(931)10=(1001 0011 0001)2

BCD奇偶校验码:

十进制BCD码奇校验码偶校验码

0 0000 00001 00000

1 0001 00010 00011

2 0010 00100 00101

3 0011 00111 00110

4 0100 01000 01001

二进制四则运算:

运算规则:

运算公式:

逻辑运算:

逻辑运算:

逻辑代数常用公式

总线

定义: 连接计算机各部件之间或各计算机直接的一束公共信息线,它是计算机中传送信息代码的公共途径

特点:

分类:

总线标准依据: 物理尺寸,引线数组,信号含义,功能和时序,工作频率,总线协议

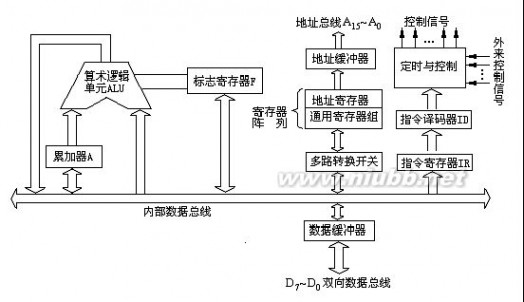

中央处理器

运算器组成:

控制器组成:

总线:

CPU运行原理图:

CPU主要性能指标:

存储器

定义: 计算机存储是存放数据和程序的设备

分类:

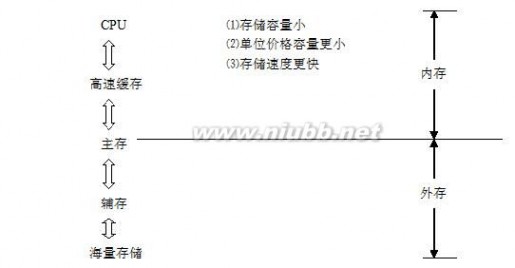

存储层次:

内存与外存的比较:

主存辅存

类型 ROM RAM 软盘 硬盘 光盘

造价 高 高 低++ 低 低+

速度 快 快 慢++ 慢 慢+

容量 小+ 小 — — —

断电 有 无 有 有 有

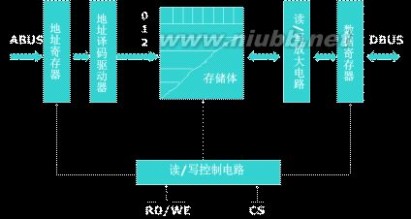

主存:

功能:

主存储器是能由CPU直接编写程序访问的存储器,它存放需要执行的程序与需要处理的数据,只能临时存放数据,不能长久保存数据

组成:

主要技术指标:

高速缓冲存储器:

定义:高速缓冲存储器是由存取速率较快的电路组成小容量存储单元,即在内存的基础上,再增加一层称为高速缓冲存储器

特点:比主存快5 ~10倍

虚拟存储器:它是建立在主存-辅存物理结构基础之上,由附加硬件装置及操作系统存储管理软件组成的一种存储体系,它将主存与辅存的地址空间统一编址,形成一个庞大的存储空间,因为实“际上CPU只能执行调入主存的程序,所以这样的存储体系成为“虚拟存储器”

ROM与RAM

RAM(随机存储器)

可读出,也可写入,随机存取,意味着存取任一单元所需的时间相同,当断电后,存储内容立即消失,称为易失性

ROM(只读存储器)

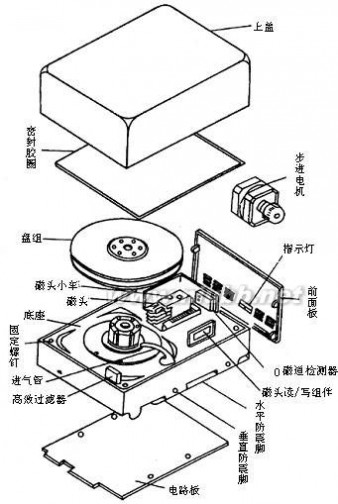

辅存(硬盘)

说明:是以铝合金圆盘为基片,上下两面涂有磁性材料而制成的磁盘

优点:体积小,重量轻,防尘性好,可靠性高,存储量大,存取速度快,但多数它们固定于主机箱内,故不便携带,价格也高于软盘

性能指标: 转速,超频性能,缓存,单碟容量,传输模式,发热量,容量,平均等待时间

硬盘组成图:

注意:

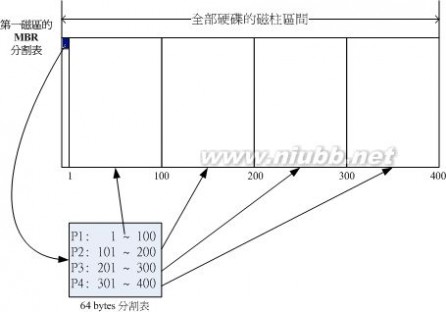

在整颗磁碟的第一个磁区特别的重要,因为他记录了整颗磁碟的重要资讯! 磁碟的第一个磁区主要记录了两个重要的资讯,分别是:

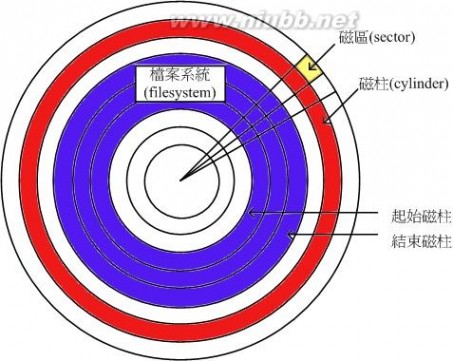

磁盘分区表(partition table):

利用参考对照磁柱号码的方式来切割硬盘分区! 在分割表所在的64 bytes容量中,总共分为四组记录区,每组记录区记录了该区段的启始与结束的磁柱号码. 若将硬盘以长条形来看,然后将磁柱以直条图来看,那么那64 bytes的记录区段有点像底下的图示:

上图中我们假设硬盘只有400个磁柱,共分割成为四个分割槽,第四个分割槽所在为第301到400号磁柱的范围.

由於分割表就只有64 bytes而已,最多只能容纳四笔分割的记录, 这四个分割的记录被称为主要(Primary)或延伸(Extended)分割槽. 根据上面的图示与说明,我们可以得到几个重点资讯:

总结:

输入/输出设备

输入设备

分类:

键盘分类(以接口类型):

鼠标分类:

语音输入设备: 主要部分: 输入器 , 模数转换器 , 语音识别器

输出设备

打印机:

显示器:

输入输出设备接口和控制方式

输入输出设备接口:

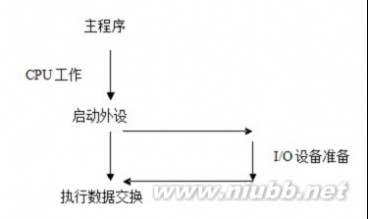

输入输出控制方式:

计算机的时标系统

时序控制方式:

同步控制方式:

异步控制方式:

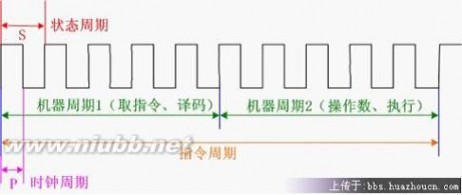

三级时标系统:

图像显示:

指令周期公式:

指令周期 = 时钟周期*组成一个机械周期所需T的个数*组成一个指令周期所需M个数

本文标题:计算机组成原理-计算机组成原理07-运算方法--并行加法器61阅读| 精彩专题| 最新文章| 热门文章| 苏ICP备13036349号-1