一 : OP07中文资料

登陆http://www.61k.com功参加活动,即可获得千元现金

op07中文资料

时间:2009-05-16 07:42:22 来源:资料室 作者:

op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。

特点:

超低偏移: 150μV最大 。

低输入偏置电流: 1.8nA 。

低失调电压漂移: 0.5μV/℃ 。

超稳定,时间: 2μV/month最大

高电源电压范围: ±3V至±22V

工作电源电压范围是±3V~±18V;OP07完全可以用单电源供电,你说的+5V,-5V绝对没有问题,用单+5V也可以供电,但是线性区间太小,单电源供电,模拟地在1/2 VCC. 建议电源最好>8V,否则线性区实在太小,放大倍数无法做大,一不小心,就充顶饱和了。我一直用+12V,-12V双电源供电。

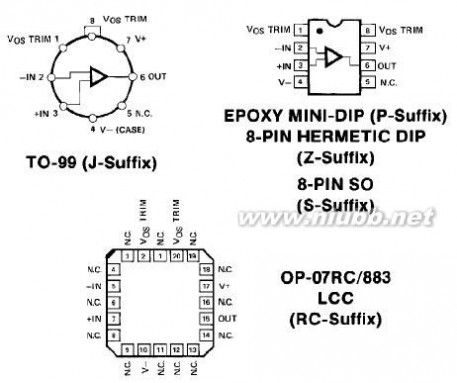

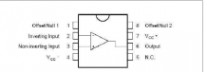

图1 OP07外型图片

登陆http://www.61k.com功参加活动,即可获得千元现金

登陆http://www.61k.com功参加活动,即可获得千元现金

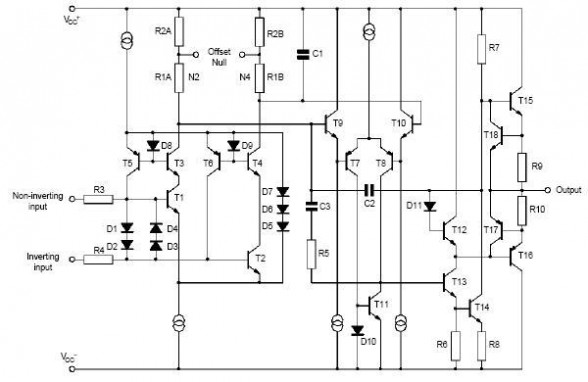

图2 OP07 管脚图 OP07芯片引脚功能说明:

1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚 6为输出,7接电源+

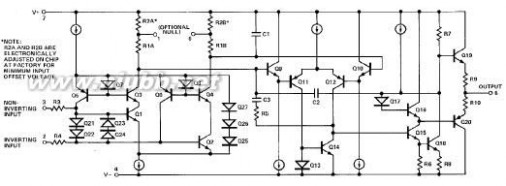

图3 OP07内部电路图

ABSOLUTE MAXIMUM RATINGS 最大额定值

Sym

bol

符号 Parameter参数 Value数值 Unit 单位

登陆http://www.61k.com功参加活动,即可获得千元现金

登陆http://www.61k.com功参加活动,即可获得千元现金

VCC Vid Vi Toper Tstg

Supply Voltage 电源电压

Differential Input Voltage差分输入电压 Input Voltage 输入电压

Operating Temperature 工作温度

±22 ±30 ±22 -40 +105 -65 +150

to to

V V V ℃

Storage Temperature 贮藏温度

℃

电气特性

虚拟通道连接= ± 15V , Tamb = 25 ℃(除非另有说明)

Symbol符号

Parameter 参数及测试条件

最小

典型 60

最大

Unit 单位

150 250

Vio

Input Offset Voltage 输入失调电压0℃ ≤ Tamb ≤ +70℃

-

μV

Long Term Input Offset Voltage Stability-(note 1) 长期输入偏置电压的稳定性

- 0.4 2 1.8

μV/Mo

DVio Input Offset Voltage Drift 输入失调电压漂移 - 0.5

μV/℃

Iio Input Offset Current输入失调电流 0℃≤Tamb≤ +70℃ - 0.8

6 8

nA

DIio Input Offset Current Drift 输入失调电流漂移 - 15 1.8

50

pA/℃

Iib Input Bias Current输入偏置电流 0℃≤Tamb ≤ +70℃ -

7 9

nA

DIib Ro Rid

Input Bias Current Drift 输入偏置电流漂移 Open Loop Output Resistance 开环输出电阻 Differential Input Resistance 差分输入电阻

- - -

15 60 33

50 - -

pA/℃ Ω MΩ

登陆http://www.61k.com功参加活动,即可获得千元现金

登陆http://www.61k.com功参加活动,即可获得千元现金

Ric

Common Mode Input Resistance 共模输入电阻 Input Common Mode Voltage Range输入共模电压范围 0℃ ≤ Tamb ≤ +70℃

- ±13 ±13

120

-

dB

120 ±1

3.5

-

GΩ

Vicm - V

CMR

Common Mode Rejection Ratio (Vi =Vicm min)共模抑制比 0℃ ≤ Tamb ≤ +70℃

100 97

SVR

Supply Voltage Rejection Ratio 电源电压抑制比(VCC = ±3to ±18V) 0℃ ≤ Tamb ≤ +70℃

VCC = ±15, RL =2KΩ,VO =

Large

Signal ±10V,

0℃ ≤ Tamb ≤ +105℃

VCC = ±3V, RL = 500W,VO = ±0.5V RL = 10KΩ

90 86 120 100 100 ±12 ±11.5

±11 - -

104

-

dB

400 400 ±13 ±12.8 ±12 - 0.17 0.5 2.7

- - -

V/mV

Avd Voltage Gain 大信号电压增益

Vopp

Output 摆幅

Voltage

Swing 输出电压

RL= 2kΩ RL= 1KΩ

0℃ ≤ Tamb ≤ +70℃ RL =2KΩ

- V

SR GBP

Slew Rate 转换率(RL =2KΩ,CL = 100pF)

Gain Bandwidth Product 带宽增益(RL =2KΩ,CL = 100pF, f = 100kHz)

Supply Current -(no load) 电源电流(无负载) 0℃ ≤ Tamb ≤ +70℃ VCC = ±3V

- - 5 6 1.3 20 13.5 11.5 0.9 0.3

V/μS MHz

Icc - 0.67

mA

f = 10Hz

Equivalent Input

en

Noise Voltage等效输入噪声电压

f = 1kHz

- 11

f = 100Hz - 10.5

√Hz

- 10

Equivalent Input f = 10Hz

in

Noise

Current

f = 100Hz

等效输入噪声电流

- -

0.3 0.2

√Hz

登陆http://www.61k.com功参加活动,即可获得千元现金

登陆http://www.61k.com功参加活动,即可获得千元现金

f = 1kHz - 0.1 0.

2

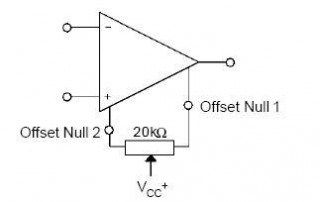

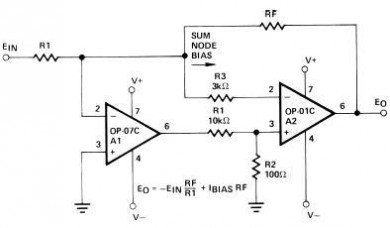

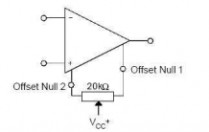

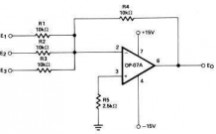

图4 输入失调电压调零电路

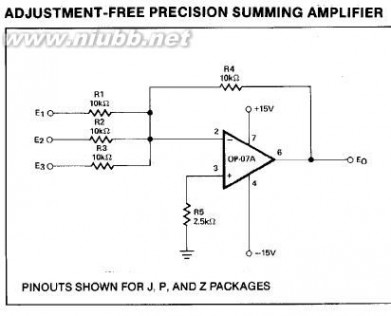

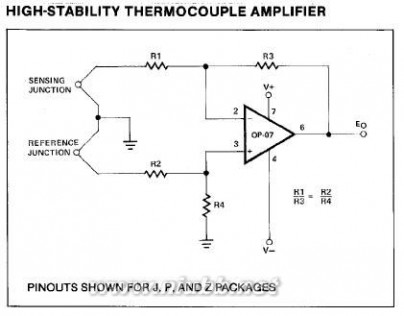

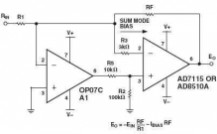

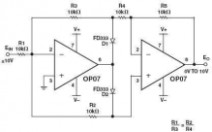

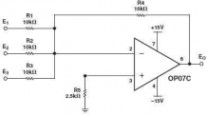

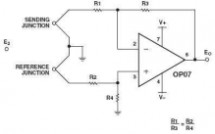

应用电路图:

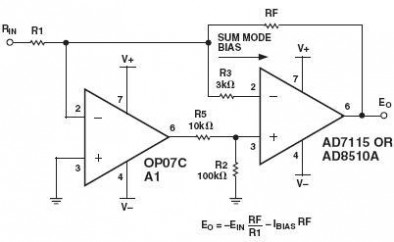

图5 典型的偏置电压试验电路

登陆http://www.61k.com功参加活动,即可获得千元现金

登陆http://www.61k.com功参加活动,即可获得千元现金

图6 老化电路

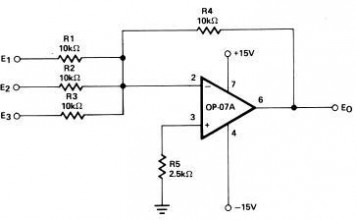

图7 典型的低频噪声放大电路

登陆http://www.61k.com功参加活动,即可获得千元现金

登陆http://www.61k.com功参加活动,即可获得千元现金

图8 高速综合放大器

图9 选择偏移零电路

图10 调整精度放大器

登陆http://www.61k.com功参加活动,即可获得千元现金

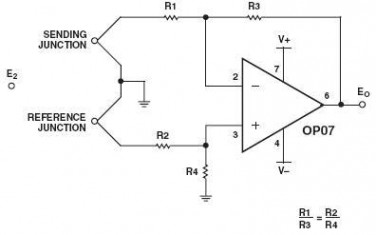

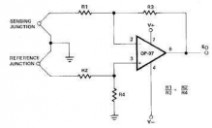

登陆http://www.61k.com功参加活动,即可获得千元现金 图11 高稳定性的热电偶放大器

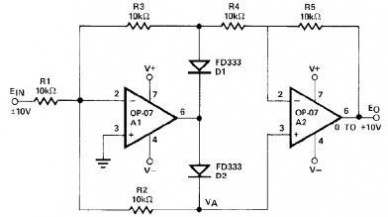

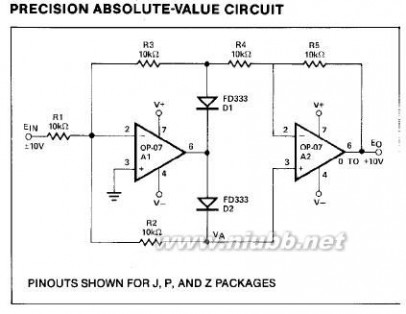

图12 精密绝对值电路

以上翻译自SGS-THOMSON的OP07

登陆http://www.61k.com功参加活动,即可获得千元现金

二 : op07管脚图介绍与pdf中文资料

OP07是高精度低失调电压的精密运放集成电路,用于微弱信号的放大,如果使用双电源.能达到最好的放大效果下面介绍一下他的引脚图资料。

op07管脚图

OP07 pdf 中文资料下载:http://www.alldatasheet.com/view.jsp?Searchword=OP07

op07介绍(www.61k.com)

1) 低的输入噪声电压幅度—0.35 μVP-P (0.1Hz ~ 10Hz)

2) 极低的输入失调电压—10 μV

3) 极低的输入失调电压温漂—0.2 μV/ ℃

4) 具有长期的稳定性—0.2 μV/MO

5) 低的输入偏置电流—± 1nA

6) 高的共模抑制比—126dB

7) 宽的共模输入电压范围—±14V

8) 宽的电源电压范围—± 3V ~± 22V

9) 可替代725、108A、741、AD510 等电路

下面是一些OP07放大电路的应用,供大家查阅。

OP07内部电路

OP07应用介绍

TD07高精度运放具有极低的输入失调电压,极低的失调电压温漂,非常低的输入噪声电压幅度及长期稳定等特点。广泛应用于稳定积分、比较器,密绝对值电路、及微弱信号的精确放大(http://www.51hei.com中有详细介绍),尤其适应于宇航、军工的应用。可和uA741,uA709,LM301,LM308, LF356,OP07,op37,max427这些运放来直接代换。

三 : op07中文资料

op07????????

??????2009-05-16 07:42:22 ???????????? ??????

op07????????????Op07????????????????????????????????????????????????????????????OP07??????????????????????????????OP07A??????25μV????????OP07????????????????????????????????????OP07????????????????????????OP07A??±2nA????????????????????OP07A??300V/mV??????????????????????????????????????????OP07????????????????????????????????????????????????????????

??????

?????????? 150μV???? ??

???????????????? 1.8nA ??

???????????????? 0.5μV/?? ??

?????????????? 2μV/month????

???????????????? ±3V??±22V

??1 OP07????????

??2 OP07 ??????

OP07??????????????????

1??8??????????(??????)??2??????????????3??????????????4??????5???? 6????????7??????+

??3 OP07?????????? ABSOLUTE MAXIMUM RATINGS ?????????? Symbol???? VCC Vid Vi Toper Tstg ????????

????????????= ± 15V ?? Tamb = 25 ?????????????????? Symbol???? Vio

Parameter ??????????????

Input Offset Voltage ????????????0?? ≤ Tamb ≤ +70??

Long Term Input Offset Voltage Stability-(note 1) ????????????????????????

Input Offset Voltage Drift ????????????????

????

???? 60

????12

0.4 0.5 0.8

16

Parameter???? Supply Voltage ????????

Differential Input Voltage???????????? Input Voltage ????????

Operating Temperature ???????? Storage Temperature ????????

Value????±22 ±30 ±22 -40 to +10-65 to +15

-

DVio Iio

- -

Input Offset Current???????????? 0??≤Tamb≤ +70?? -

DIio Iib DIib Ro Rid Ric Vicm

Input Offset Current Drift ???????????????? - 15 1.8

50 pA/?? 7 9

nA

Input Bias Current???????????? 0??≤Tamb ≤ +70?? - Input Bias Current Drift ???????????????? Open Loop Output Resistance ???????????? Differential Input Resistance ???????????? Common Mode Input Resistance ????????????

- - - -

15 60 33 120 ±13.5

50 pA/?? - - - -

? M? G? V

Input Common Mode Voltage Range???????????????? ±13 0?? ≤ Tamb ≤ +70??

Common Mode Rejection Ratio (Vi =Vicm min)?????????? 0?? ≤ Tamb ≤ +70??

Supply Voltage Rejection Ratio ??????????????(VCC = ±3to ±18V) 0?? ≤ Tamb ≤ +70??

VCC = ±15, RL =2K?,VO =

Large Signal

±10V,

0?? ≤ Tamb ≤ +105??

VCC = ±3V, RL = 500W,VO = ±0.5V RL = 10K?

±13 100 97 90 86 120 100 100 ±12 ±11.5

CMR

120

- dB

SVR

104

- dB

400 400 ±13 ±12.8

- - -

V/mV

Avd Voltage Gain ??????????????

Vopp

Output Voltage

RL= 2k?

Swing ???????????? RL= 1K?

-

±12 - 0.17 0.5

- - 5 6 1.3 20

V

0?? ≤ Tamb ≤ +70?? RL =2K? ±11

SR GBP

Slew Rate ??????(RL =2K?,CL = 100pF)

Gain Bandwidth Product ????????(RL =2K?,CL = 100pF, f = 100kHz)

Supply Current -(no load) ?????????????????? 0?? ≤ Tamb ≤ +70?? VCC = ±3V Equivalent Input

en

Noise Voltage???????????????? Equivalent Input

in

Noise Current ????????????????

- -

V/μS MHz

Icc - - - - - - -

2.7 0.67

11

mA

f = 10Hz f = 100Hz f = 1kHz f = 10Hz f = 100Hz f = 1kHz

10.5 13.5 10 0.3 0.2 0.1

11.5 0.9 0.3 0.2

√Hz

√Hz

??4 ???????????????????? ????????????

??5 ??????????????????????

??6 ????????

??7 ??????????????????????

??8 ??????????????

??9 ??????????????

??10 ??????????????

??11 ??????????????????????

??12 ??????????????

四 : DAC5682ZIRGCRG4中文资料

元器件交易网www.61k.com

www.ti.comSLLS853B–AUGUST2007–REVISEDAPRIL2008

16-BIT,1.0GSPS2x-4xINTERPOLATINGDUAL-CHANNEL

DIGITAL-TO-ANALOGCONVERTER(DAC)

FEATURES

16-BitDigital-to-AnalogConverter(DAC)1.0GSPSUpdateRate

16-BitWidebandInputLVDSDataBus–8SampleInputFIFO

–InterleavedI/QdataforDual-DACModeHighPerformance

–73dBcACLRWCDMATM1at180MHz2x-32xClockMultiplyingPLL/VCO2xor4xInterpolationFilters

–StopbandTransition0.4–0.6Fdata

–FiltersConfigurableinEitherLow-PassorHigh-PassMode

–AllowsSelectionofHigherOrderImageFs/4CoarseMixer

OnChip1.2VReference

DifferentialScalableOutput:2to20mAPackage:64-Pin9×9mmQFN

???

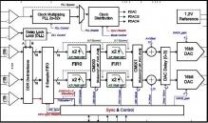

DESCRIPTION

TheDAC5682Zisadual-channel16-bit1.0GSPSdigital-to-analogconverter(DAC)withwidebandLVDSdatainput,integrated2x/4xinterpolationfilters,on-boardclockmultiplierandinternalvoltagereference.TheDAC5682Zofferssuperiorlinearity,noise,crosstalkandPLLphasenoiseperformance.TheDAC5682ZintegratesawidebandLVDSportwithon-chiptermination.Full-rateinputdatacanbetransferredtoasingleDACchannel,orhalf-rateand1/4-rateinputdatacanbeinterpolatedbyon-board2xor4xFIRfilters.EachinterpolationFIRisconfigurableineitherLow-PassorHigh-Passmode,allowingselectionofahigherorderoutputspectralimage.Anon-chipdelaylockloop(DLL)simplifiesLVDSinterfacingbyprovidingskewcontrolfortheLVDSinputdataclock.

TheDAC5682Zallowsbothcomplexorrealoutput.AnoptionalFs/4coarsemixerincomplexmodeprovidescoarsefrequencyupconversionandthedualDACoutputproducesacomplexHilbertTransformpair.AnexternalRFquadraturemodulatorthenperformsthefinalsinglesidebandup-conversion.TheDAC5682Zischaracterizedforoperationovertheindustrialtemperaturerangeof–40°Cto85°Candisavailableina64-pinQFNpackage.Othersingle-channelmembersofthefamilyincludetheinterpolatingDAC5681Zandnon-interpolatingDAC5681.

???

????

APPLICATIONS

?????

CellularBaseStations

BroadbandWirelessAccess(BWA)WiMAX802.16

FixedWirelessBackhaul

CableModemTerminationSystem(CMTS)

ORDERINGINFORMATION

TA

–40°Cto85°C(1)(2)(3)

ORDERCODEDAC5682ZIRGCTDAC5682ZIRGCR

PACKAGEDRAWING/TYPE(1)(2)(3)

RGC/64QFNQuadFlatpack

No-Lead

TRANSPORTMEDIASmallTapeandReelLargeTapeandReel

QUANTITY

2502000

ThermalPadSize:7,4mm×7,4mm

MSLPeakTemperature:Level-3-260C-168HR

Forthemostcurrentpackageandorderinginformation,seethePackageOptionAddendumattheendofthisdocument,orseetheTIwebsiteatwww.ti.comPleasebeawarethatanimportantnoticeconcerningavailability,standardwarranty,anduseincriticalapplicationsofTexasInstrumentssemiconductorproductsanddisclaimerstheretoappearsattheendofthisdatasheet.

PRODUCTIONDATAinformationiscurrentasofpublicationdate.ProductsconformtospecificationsperthetermsoftheTexasInstrumentsstandardwarranty.Productionprocessingdoesnotnecessarilyincludetestingofallparameters.

Copyright?2007–2008,TexasInstrumentsIncorporated

元器件交易网www.61k.com

SLLS853B–AUGUST2007–REVISEDAPRIL2008www.ti.com

Thesedeviceshavelimitedbuilt-inESDprotection.TheleadsshouldbeshortedtogetherorthedeviceplacedinconductivefoamduringstorageorhandlingtopreventelectrostaticdamagetotheMOSgates.

FUNCTIONALBLOCKDIAGRAM

V(1V(3V

V2SubmitDocumentationFeedback

ProductFolderLink(s):DAC5682Z

Copyright?2007–2008,TexasInstrumentsIncorporated

www.ti.comSLLS853B–AUGUST2007–REVISEDAPRIL2008

DAC5682ZRGCPACKAGE(TOPVIEW)

IOUTB1

IOUTB2

IOUTA1AVDD

52

51

IOUTA2

AVDDEXTLO

EXTIO

53

50

64

63

62

61

60

59

58

57

56

55

54

49

RESETB

DVDD

DVDD

BIASJ

AVDD

LPF

AVDD

AVDD

CLKVDDCLKINCLKINCGNDSYNCPSYNCND15PD15NIOVDDDVDDD14PD14ND13PD13ND12PD12N

12345678910111213141516

48474645444342

SDENBSCLKSDIOSDOVFUSED0ND0PD1ND1PDVDDD2ND2PD3ND3PD4ND4P

DAC5682Z

414039383736353433

31

28

17

18

20

21

29

23

24

25

26

D11N

27

22

DCLKN

D7N

D10N

D9N

D8N

D6N

30

19

D11P

D10P

TERMINALFUNCTIONS

TERMINALNAMEAVDDBIASJCLKINCLKINCCLKVDD

NO.51,54,55,59,62

572317,11,13,15,17,19,21,23,27,29,31,33,35,37,40,

42

I/OIOIII

Analogsupplyvoltage.(3.3V)

Full-scaleoutputcurrentbias.For20mAfull-scaleoutputcurrent,connecta960?resistortoGND.Positiveexternalclockinputwithaself-biasofapproximatelyCLKVDD/2.WiththeclockmultiplierPLLenabled,CLKINprovideslowerfrequencyreferenceclock.IfthePLLisdisabled,CLKINdirectlyprovidesclockforDACupto1GHz.

Complementaryexternalclockinput.(SeetheCLKINdescription)Internalclockbuffersupplyvoltage.(1.8V)

LVDSpositiveinputdatabits0through15.Eachpositive/negativeLVDSpairhasaninternal100?

terminationresistor.Orderofbuscanbereversedviarev_busbitinCONFIG5register.DataformatrelativetoDCLKP/NclockisDoubleDataRate(DDR)withtwodatasamplesinputperDCLKP/Nclock.Indual-channelmode,datafortheA-channelisinputwhileDCLKPishigh.

D15Pismostsignificantdatabit(MSB)–pin7D0Pisleastsignificantdatabit(LSB)–pin42

DESCRIPTION

D[15..0]PI

DCLKP

Copyright?2007–2008,TexasInstrumentsIncorporatedSubmitDocumentationFeedback

ProductFolderLink(s):DAC5682Z

D5N

D7P

D9P

D8P

D5P

D6P

32

3

元器件交易网www.61k.com

SLLS853B–AUGUST2007–REVISEDAPRIL2008www.ti.com

TERMINALFUNCTIONS(continued)

4SubmitDocumentationFeedback

ProductFolderLink(s):DAC5682ZCopyright?2007–2008,TexasInstrumentsIncorporated

www.ti.comSLLS853B–AUGUST2007–REVISEDAPRIL2008

ABSOLUTEMAXIMUMRATINGS

overoperatingfree-airtemperaturerange(unlessotherwisenoted)

DVDD(2)VFUSE(2)

Supplyvoltagerange

CLKVDD(2)AVDD(2)IOVDD(2)AVDDtoDVDDCLKVDDtoDVDDIOVDDtoAVDD

D[15..0]P,D[15..0]N,SYNCP,SYNCN

Supplyvoltagerange

DCLKP,DCLKN

(2)

(2)

(1)

VALUE–0.5to2.3–0.5to2.3–0.5to2.3–0.5to4–0.5to4–2to2.6–0.5to0.5–0.5to0.5–0.5toDVDD+0.5

–0.3to2.1–0.5toCLKVDD+0.5

(2)

UNITVVVVVVVVVVVVVVmAmA°C°C

CLKIN,CLKINC(2)

SDO,SDIO,SCLK,SDENB,RESETBIOUTA1/B1,IOUTA2/B2

Peakinputcurrent(anyinput)Peaktotalinputcurrent(allinputs)

Operatingfree-airtemperaturerange,TA:DAC5682ZIStoragetemperaturerange(1)(2)

(2)

–0.5toIOVDD+0.5–0.5toAVDD+0.5–0.5toAVDD+0.5

20–30–40To85–65To150

LPF,EXTIO,EXTLO,BIASJ(2)

Stressesbeyondthoselistedunderabsolutemaximumratingsmaycausepermanentdamagetothedevice.Thesearestressratingsonly,andfunctionaloperationoftheseoranyotherconditionsbeyondthoseindicatedunderrecommendedoperatingconditionsisnotimplied.Exposuretoabsolute-maximum-ratedconditionsforextendedperiodsmayaffectdevicereliability.MeasuredwithrespecttoGND.

THERMALCHARACTERISTICS

overoperatingfree-airtemperaturerange(unlessotherwisenoted)

THERMALCONDUCTIVITY

TJθJAθJCθJP(1)

Maximumjunctiontemperature

(1)

64ldQFN125201670.2

UNIT°C°C/W°C/W°C/W

Thetajunction-to-ambient(stillair)Thetajunction-to-ambient(150lfm)Thetajunction-to-caseThetajunction-to-pad

AirfloworheatsinkingreducesθJAandmayberequiredforsustainedoperationat85°undermaximumoperatingconditions.

Copyright?2007–2008,TexasInstrumentsIncorporatedSubmitDocumentationFeedback

ProductFolderLink(s):DAC5682Z

5

元器件交易网www.61k.com

SLLS853B–AUGUST2007–REVISEDAPRIL2008www.ti.com

ELECTRICALCHARACTERISTICS—DCSPECIFICATION

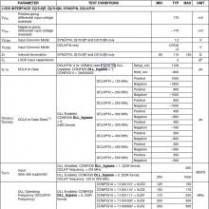

overoperatingfree-airtemperaturerange,AVDD=3.3V,CLKVDD=1.8V,IOVDD=3.3V,DVDD=1.8V,IoutFS=20mA(unlessotherwisenoted)

PARAMETER

ResolutionDCACCURACY(1)INLDNL

IntegralnonlinearityDifferentialnonlinearityCoursegainlinearityOffseterrorGainerrorGainerrorGainmismatch

Minimumfullscaleoutputcurrent

(2)(2)

TESTCONDITIONSMIN16

TYPMAXUNITBits

1LSB=IOUTFS/216

±4±2±0.04

LSB

ANALOGOUTPUT

LSB%FSR%FSR%FSR2

220

IOUTFS=20mA

AVDD–0.5V

3005

1.14

(4)

Midcodeoffset

WithoutinternalreferenceWithinternalreference

Withinternalreference,dualDAC

–2

0.0110.7

%FSRmA

MaximumfullscaleoutputcurrentOutputCompliancerange(3)OutputresistanceOutputcapacitance

REFERENCEOUTPUTVref

ReferencevoltageReferenceoutputcurrent

REFERENCEINPUTVEXTIO

InputvoltagerangeInputresistanceSmallsignalbandwidthInputcapacitance

TEMPERATURECOEFFICIENTS

OffsetdriftGaindrift

Referencevoltagedrift

POWERSUPPLY

Analogsupplyvoltage,AVDDDigitalsupplyvoltage,DVDDClocksupplyvoltage,CLKVDDI/Osupplyvoltage,IOVDD

I(AVDD)I(DVDD)I(CLKVDD)I(IOVDD)

AnalogsupplycurrentDigitalsupplycurrentClocksupplycurrentIOsupplycurrent

AVDD+0.5V

Vk?pF

1.2100

1.26VnA

0.1

1

CONFIG6:BiasLPF_AandBiasLPF_B=1CONFIG6:BiasLPF_AandBiasLPF_B=0

95472100

1.25VM?kHzpFppmofFSR/°CppmofFSR/°Cppm/°C

±1

WithoutinternalreferenceWithinternalreference

±15±30±8

3.01.711.713.0

3.31.81.83.3133

Mode4(below)

4554512

3.62.152.153.6

VVVVmAmAmAmA

(1)(2)(3)(4)6

MeasureddifferentialacrossIOUTA1andIOUTA2orIOUTB1andIOUTB2with25?eachtoAVDD.Nominalfull-scalecurrent,IoutFS,equals16×IBIAScurrent.

ThelowerlimitoftheoutputcomplianceisdeterminedbytheCMOSprocess.Exceedingthislimitmayresultintransistorbreakdown,resultinginreducedreliabilityoftheDAC5682Zdevice.Theupperlimitoftheoutputcomplianceisdeterminedbytheloadresistorsandfull-scaleoutputcurrent.Exceedingtheupperlimitadverselyaffectsdistortionperformanceandintegralnonlinearity.Useanexternalbufferamplifierwithhighimpedanceinputtodriveanyexternalload.

SubmitDocumentationFeedback

ProductFolderLink(s):DAC5682Z

Copyright?2007–2008,TexasInstrumentsIncorporated

www.ti.comSLLS853B–AUGUST2007–REVISEDAPRIL2008

ELECTRICALCHARACTERISTICS—DCSPECIFICATION(continued)

overoperatingfree-airtemperaturerange,AVDD=3.3V,CLKVDD=1.8V,IOVDD=3.3V,DVDD=1.8V,IoutFS=20mA(unlessotherwisenoted)

PARAMETER

I(AVDD)I(DVDD)I(CLKVDD)I(IOVDD)

Sleepmode,AVDDsupplycurrentSleepmode,DVDDsupplycurrentSleepmode,CLKVDDsupplycurrent

Sleepmode,IOVDDsupplycurrentAVDD+IOVDDcurrent,3.3VDVDD+CLKVDDcurrent,1.8VPowerDissipation

AVDD+IOVDDcurrent,3.3VDVDD+CLKVDDcurrent,1.8VPowerDissipation

AVDD+IOVDDcurrent,3.3VDVDD+CLKVDDcurrent,1.8V

P

PowerDissipation

AVDD+IOVDDcurrent,3.3VDVDD+CLKVDDcurrent,1.8VPowerDissipation

AVDD+IOVDDcurrent,3.3VDVDD+CLKVDDcurrent,1.8VPowerDissipation

AVDD+IOVDDcurrent,3.3VDVDD+CLKVDDcurrent,1.8VPowerDissipation

PSSRT

PowersupplyrejectionratioOperatingrange

Mode1:2X2,PLL=OFF,CLKIN=983.04MHzFDAC=983.04MHz,IF=184.32MHzDACAandDACBON,4carrierWCDMAMode2:2X2,PLL=ON(8X),CLKIN=122.88MHz

FDAC=983.04MHz,IF=184.32MHzDACAandDACBON,4carrierWCDMA

Mode3:2X4,CMIX0=Fs/4,PLL=OFF,CLKIN=983.04MHz

FDAC=983.04MHz,IF=215.04MHzDACAandDACBON,4carrierWCDMAMode4:2X4,CMIX0=Fs/4,PLL=ON(8X),CLKIN=122.88MHz

FDAC=983.04MHz,IF=215.04MHzDACAandDACBON,4carrierWCDMA

Mode5:2X2,CMIX0=Fs/4,PLL=OFF,CLKIN=983.04MHz

FDAC=983.04MHz,DigitalLogicDisabledDACAandDACBSLEEP,StaticDataPatternMode6:2X4,PLL=OFF,CLKIN=OFFFDAC=OFF,DigitalLogicDisabled

DACAandDACB=SLEEP,StaticDataPattern

–2–40

Mode6(below)

TESTCONDITIONS

MIN

TYP1.01.52.52.01354501255145485135013548013101455051400

51853503.04.017.0

30.0851600MAX

UNITmAmAmAmAmAmAmWmAmAmWmAmAmWmAmAmWmAmAmWmAmAmW°C

0.2%FSR/V

Copyright?2007–2008,TexasInstrumentsIncorporatedSubmitDocumentationFeedback

ProductFolderLink(s):DAC5682Z

7

元器件交易网www.61k.com

SLLS853B–AUGUST2007–REVISEDAPRIL2008www.ti.com

ELECTRICALCHARACTERISTICS—ACSPECIFICATION(1)

Overrecommendedoperatingfree-airtemperaturerange,AVDD,IOVDD=3.3V,CLKVDD,DVDD=1.8V,IOUTFS=20mA,4:1transformeroutputtermination,50?doublyterminatedload(unlessotherwisenoted)

PARAMETER

ANALOGOUTPUTfCLKts(DAC)tpdtr(IOUT)tf(IOUT)

Maximumoutputupdaterate

Outputsettlingtimeto0.1%

OutputpropagationdelayOutputrisetime10%to90%

Outputfalltime90%to10%

1X1,PLLoff,CLKIN=500MHz,DACAon,IF=5.1MHz,FirstNyquistZone<fDATA/2

SFDR

Spuriousfreedynamicrange

2X2,PLLoff,CLKIN=1000MHz,DACAandDACBon,IF=5.1MHz,FirstNyquistZone<fDATA/2

2X2,PLLoff,CLKIN=1000MHz,DACAandDACBon,IF=20.1MHz,FirstNyquistZone<fDATA/2

2X2,PLLoff,CLKIN=500MHZ,DACAandDACBon,Singletone,0dBFS,IF=20.1MHz

2X2,PLLoff,CLKIN=1000MHZ,DACAandDACBon,Singletone,0dBFS,IF=20.1MHz

2X2,PLLoff,CLKIN=1000MHZ,DACAandDACBon,Singletone,0dBFS,IF=70.1MHz

2X4,PLLoff,CLKIN=1000MHZ,DACAandDACBon,Singletone,0dBFS,IF=180MHz

2X2CMIX,PLLoff,CLKIN=1000MHZ,DACAandDACBon,Singletone,0dBFS,IF=300.2MHz

2X2,PLLoff,CLKIN=1000MHZ,DACAandDACBon,Fourtone,each-12dBFS,IF=24.7,24.9,25.1and25.3MHz2X2,PLLoff,CLKIN=1000MHZ,DACAandDACBon,IF=20.1and21.1MHz

IMD3

Third-ordertwo-tone

intermodulation(eachtoneat–6dBFS)

2X2,PLLoff,CLKIN=1000MHZ,DACAandDACBon,IF=70.1and71.1MHz

2X2CMIX,PLLoff,CLKIN=1000MHZ,DACAandDACBon,IF=150.1and151.1MHz

IMD

Four-toneintermodulation(eachtoneat–12dBFS)

2X2CMIX,PLLoff,CLKIN=1000MHz,DACAandDACBon,fOUT=298.4,299.2,300.8and301.6MHz

Singlecarrier,baseband,2X2,PLLoff,CLKIN=983.04MHz,DACAandDACBon(3)

(2)

TESTCONDITIONSMINTYPMAXUNIT

1000

Transition:Code0x0000to0xFFFF

10.42.5220220

MSPSnsnspsps

ACPERFORMANCE

818077736963

dBc

60607381726464

80

8373

dBc

666393

dBc

85

dBcdBcdBc

SNRSignal-to-noiseratio

ACLR

Adjacentchannelleakageratio

Singlecarrier,IF=180MHz,2X2,PLLoff,CLKIN=983.04MHz,DACAandDACBonFourcarrier,IF=180MHz,2X2CMIX,PLLoff,CLKIN=983.04MHz,DACAandDACBonFourcarrier,IF=275MHz,2X2CMIX,PLLoff,CLKIN=983.04MHz,DACAandDACBon

Noisefloor

(4)

50-MHzoffset,1-MHzBW,SingleCarrier,baseband,2X2,PLLoff,CLKIN=983.04

50-MHzoffset,1-MHzBW,FourCarrier,baseband,2X2,PLLoff,CLKIN=983.04.

(1)(2)(3)(4)Measuredsingle-endedinto50?load.

W-CDMAwith3.84MHzBW,5-MHzspacing,centeredatIF.TESTMODEL1,10msValidover25°Cto85°C

Carrierpowermeasuredin3.84MHzBW.

8SubmitDocumentationFeedback

ProductFolderLink(s):DAC5682Z

Copyright?2007–2008,TexasInstrumentsIncorporated

www.ti.comSLLS853B–AUGUST2007–REVISEDAPRIL2008

ELECTRICALCHARACTERISTICS(DIGITALSPECIFICATIONS)

overrecommendedoperatingfree-airtemperaturerange,AVDD,IOVDD=3.3V,CLKVDD,DVDD=1.8V.

(1)

Positiveskew:Clockaheadofdata.Negativeskew:Dataaheadofclock.

Copyright?2007–2008,TexasInstrumentsIncorporatedSubmitDocumentationFeedback

ProductFolderLink(s):DAC5682Z

9

元器件交易网www.61k.com

SLLS853B–AUGUST2007–REVISEDAPRIL2008www.ti.com

ELECTRICALCHARACTERISTICS(DIGITALSPECIFICATIONS)(continued)

overrecommendedoperatingfree-airtemperaturerange,AVDD,IOVDD=3.3V,CLKVDD,DVDD=1.8V.

PARAMETER

VIHVILIIHIILCI

High-levelinputvoltageLow-levelinputvoltageHigh-levelinputcurrentLow-levelinputcurrentCMOSInputcapacitance

Iload=–100μA

VOH

SDO,SDIO

Iload=–2mAIload=100μA

VOLts(SDENB)ts(SDIO)th(SDIO)t(SCLK)t(SCLKH)t(SCLK)td(Data)tRESET

SDO,SDIO

Setuptime,SDENBtorisingedgeofSCLKSetuptime,SDIOvalidtorisingedgeofSCLKHoldtime,SDIOvalidtorisingedgeofSCLKPeriodofSCLKHightimeofSCLKLowtimeofSCLKDataoutputdelayafterfallingedgeofSCLKMinimumRESETBpulsewidthDutycycleDifferentialvoltageCLKIN/CLKINCinputcommonmode

0.5

Iload=2mA

201051004040

10250.22xIOVDD

TESTCONDITIONS

MIN20–40–40

5IOVDD–0.20.8xIOVDD

0.2

TYP30

0.84040MAX

UNITVVμAμApFVVVVnsnsnsnsnsnsnsns

CMOSINTERFACE:SDO,SDIO,SCLK,SDENB,RESETB

CLOCKINPUT(CLKIN/CLKINC)

50%1

CLKVDD

÷2

VV

10SubmitDocumentationFeedback

ProductFolderLink(s):DAC5682Z

Copyright?2007–2008,TexasInstrumentsIncorporated

www.ti.comSLLS853B–AUGUST2007–REVISEDAPRIL2008ELECTRICALCHARACTERISTICS(DIGITALSPECIFICATIONS)(continued)

overrecommendedoperatingfree-airtemperaturerange,AVDD,IOVDD=3.3V,CLKVDD,DVDD=1.8V.

PARAMETER

PHASELOCKEDLOOP

DACoutputat600kHzoffset,100MHz,0-dBFStone,

2X4,fDATA=250MSPS,CLKIN/C=250MHz,

PLL_m='00111',PLL_n='001',VCO_div2=0,

PLL_range='1111',PLL_gain='00'

DACoutputat6MHzoffset,100MHz,0-dBFStone,

2X4,fDATA=250MSPS,CLKIN/C=250MHz,

PLL_m='00111',PLL_n='001',VCO_div2=0,

PLL_range='1111',PLL_gain='00'

PLL_gain='00',PLL_range='0000'(0)

PLL_gain='01',PLL_range='0001'(1)

PLL_gain='01',PLL_range='0010'(2)

PLL_gain='01',PLL_range='0011'(3)

PLL_gain='01',PLL_range='0100'(4)

PLL_gain='10',PLL_range='0101'(5)

PLL_gain='10',PLL_range='0110'(6)

PLL_gain='10',PLL_range='0111'(7)

PLL/VCOOperating

Frequency,

TypicalVCOGainPLL_gain='10',PLL_range='1000'(8)

PLL_gain='10',PLL_range='1001'(9)

PLL_gain='11',PLL_range='1010'(A)

PLL_gain='11',PLL_range='1011'(B)

PLL_gain='11',PLL_range='1100'(C)

PLL_gain='11',PLL_range='1101'(D)

PLL_gain='11',PLL_range='1110'(E)

PLL_gain='11',PLL_range='1111'(F)

PFDMaximum

Frequency1602202903004002604802405602106202706902507402407902208402108802509202309602201000210103020010601901601090107010401020990940880850820780740620570520460–125dBc/Hz–146290MHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzMHz/VMHzTESTCONDITIONSMINTYPMAXUNITPhasenoiseCopyright?2007–2008,TexasInstrumentsIncorporatedSubmitDocumentationFeedback

ProductFolderLink(s):DAC5682Z11

本文标题:op07中文资料-OP07中文资料61阅读| 精彩专题| 最新文章| 热门文章| 苏ICP备13036349号-1