一 : 8位双向移位寄存器电路设计

目录

摘要 .................................................................................................................................................. 1

1 多功能双向移位寄存器 ............................................................................................................... 2

1.1 基本工作原理 .................................................................................................................... 2

1.2 基本实现方案 .................................................................................................................... 2

2 电路图设计................................................................................................................................... 4

2.1 电路结构............................................................................................................................ 4

2.2 真值表................................................................................................................................ 4

3 Verilog描述8位双向移位寄存器 ............................................................................................... 6

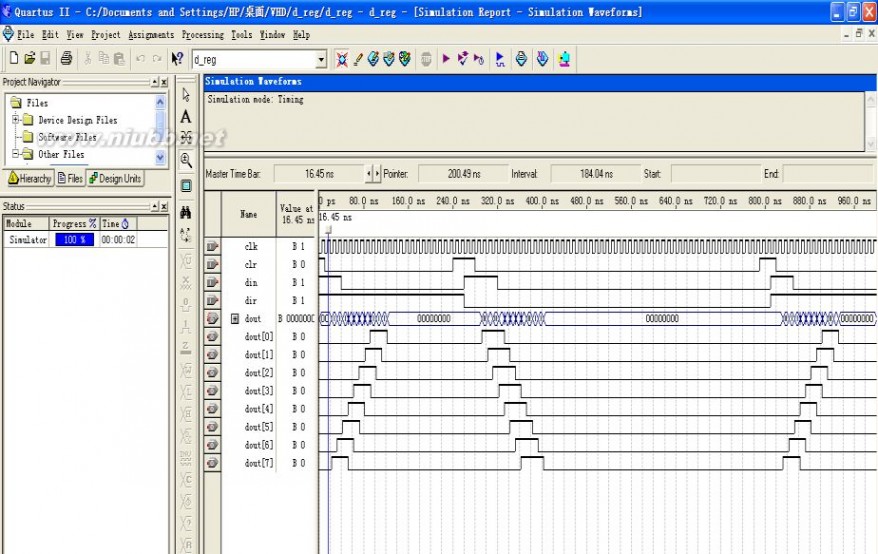

4 程序仿真....................................................................................................................................... 8

5 总结 ............................................................................................................................................ 10

参考文献......................................................................................................................................... 11

武汉理工大学《能力拓展训练》说明书

摘要

移位寄存器是基本的同步时序电路,基本的移位寄存器可以实现数据的串行/并行或并行/串行的转换、数值运算以及其他数据处理功能。在本设计中,使用硬件描述语言Verilog,在EDA工具QuartussII中,设计8位双向移位寄存器硬件电路,根据设计语言进行功能时序仿真,验证设计的正确性与可行性。

关键字:Verilog QuartusII

移位寄存器 1

二 : 四位双向移位寄存器

实验五 四位双向移位寄存器

一、实训目的

1.巩固编译、仿真VHDL文件的方法。(www.61k.com) 2.掌握VHDL程序顺序语句的应用。 3.掌握四位双向移位寄存器的工作原理。 二、实训器材

计算机与Quartus Ⅱ工具软件。 三、实训指导 (一) 实训原理

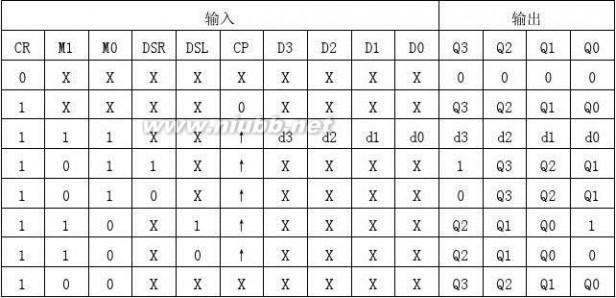

四位双向移位寄存器真值表如表5-1所示。

表5-1 四位双向移位寄存器的真值表

(二)实训步骤 1.设计输入VHDL文件 (1)建立工程项目。 (2)建立VHDL文件。

(3)设计输入VHDL文件,可用IF语句或CASE语句等顺序语句设计。 VHDL代码如下:

双向移位寄存器 四位双向移位寄存器

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY YWJCQ4 IS

PORT(M:IN STD_LOGIC_VECTOR(1 DOWNTO 0); D:IN STD_LOGIC_VECTOR(3 DOWNTO 0); CR,CP,DSR,DSL:IN STD_LOGIC;

Q:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0)); END YWJCQ4;

ARCHITECTURE W OF YWJCQ4 IS

BEGIN

PROCESS(CR,CP,DSR,DSL,M,D)

BEGIN

IF CR='0' THEN Q<="0000";

ELSIF (CP='1' AND CP'EVENT) THEN CASE M IS

WHEN "11"=>Q<=D;

WHEN "01"=>Q<=DSR&Q(3 DOWNTO 1); WHEN "10"=>Q<=Q(2 DOWNTO 0)&DSL; WHEN OTHERS=>Q<=Q;

END CASE;

END IF;

END PROCESS;

END W;

2.编译仿真VHDL文件

(1)编译VHDL文件。[www.61k.com]

如果有错误,检查并纠正错误,直至最后通过。

(2)仿真VHDL文件。

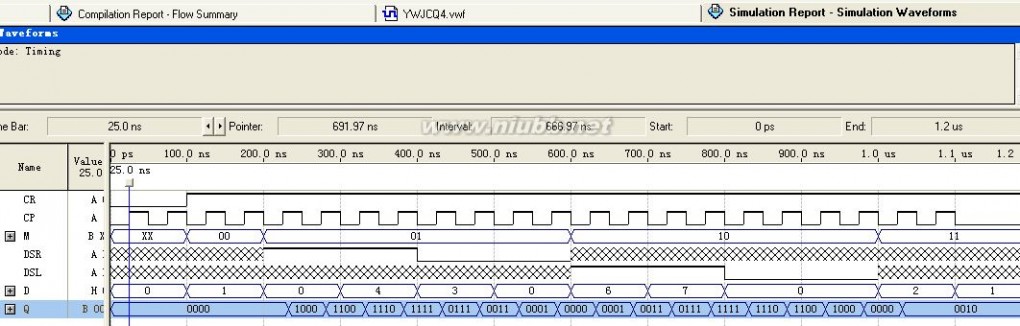

认真核对输入/输出波形,检查设计的功能是否正确。 四位双向移位寄存器的仿真波形图如图5-1所示。

双向移位寄存器 四位双向移位寄存器

图5-1 四位双向移位寄存器仿真波形图

四、实训总结

通过本次试验我掌握了VHDL文件的编译与仿真,同时巩固了IF语句和CASE语句的应用。(www.61k.com)

三 : 四位双向移位寄存器

实验五 四位双向移位寄存器

一、实训目的

1.巩固编译、仿真VHDL文件的方法。 2.掌握VHDL程序顺序语句的应用。 3.掌握四位双向移位寄存器的工作原理。 二、实训器材

计算机与Quartus Ⅱ工具软件。 三、实训指导 (一) 实训原理

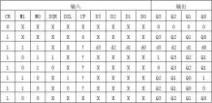

四位双向移位寄存器真值表如表5-1所示。

表5-1 四位双向移位寄存器的真值表

(二)实训步骤 1.设计输入VHDL文件 (1)建立工程项目。 (2)建立VHDL文件。

(3)设计输入VHDL文件,可用IF语句或CASE语句等顺序语句设计。 VHDL代码如下:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY YWJCQ4 IS

PORT(M:IN STD_LOGIC_VECTOR(1 DOWNTO 0); D:IN STD_LOGIC_VECTOR(3 DOWNTO 0); CR,CP,DSR,DSL:IN STD_LOGIC;

Q:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0)); END YWJCQ4;

ARCHITECTURE W OF YWJCQ4 IS

BEGIN

PROCESS(CR,CP,DSR,DSL,M,D)

BEGIN

IF CR='0' THEN Q<="0000";

ELSIF (CP='1' AND CP'EVENT) THEN CASE M IS

WHEN "11"=>Q<=D;

WHEN "01"=>Q<=DSR&Q(3 DOWNTO 1); WHEN "10"=>Q<=Q(2 DOWNTO 0)&DSL; WHEN OTHERS=>Q<=Q;

END CASE;

END IF;

END PROCESS;

END W;

2.编译仿真VHDL文件

(1)编译VHDL文件。

如果有错误,检查并纠正错误,直至最后通过。

(2)仿真VHDL文件。

认真核对输入/输出波形,检查设计的功能是否正确。 四位双向移位寄存器的仿真波形图如图5-1所示。

图5-1 四位双向移位寄存器仿真波形图

四、实训总结

通过本次试验我掌握了VHDL文件的编译与仿真,同时巩固了IF语句和CASE语句的应用。

四 : 双向移位寄存器

学生实验报告

实验课名称:VHDL硬件描述语言 实验项目名称:双向移位寄存器 专业名称:电子科学与技术 班

学级: 号: 学生姓名: 教师姓名: 2010年__11__月__13__日

双向移位寄存器 双向移位寄存器

实验日期年日 实验室名称______________成绩_____

一、实验名称:

双向移位寄存器

二、实验目的与要求:

设计一个双向移位寄存器,理解移位寄存器的工作原理。[www.61k.com)掌握串

入/并出端口控制的描述方法。

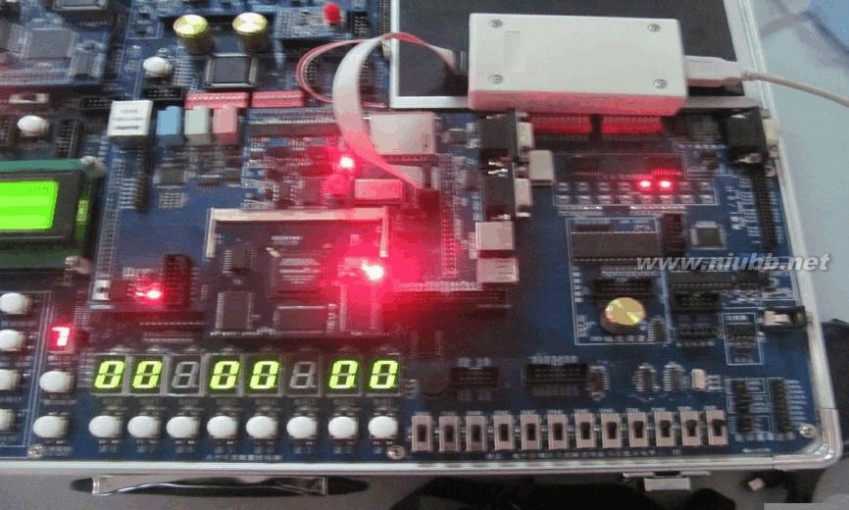

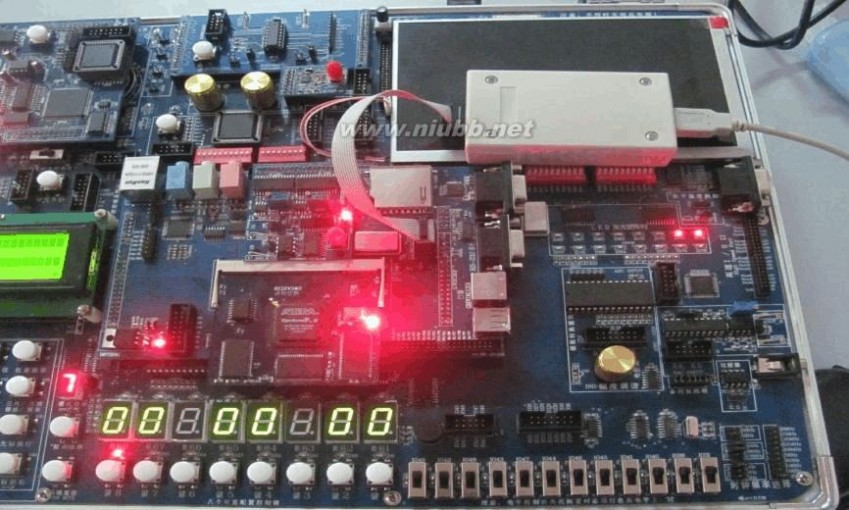

在QuartusII上进行功能和时序仿真,之后通过器件及其端口配置

下载程序到SOPC开发平台中。

1,用实验平台的按键实现时钟控制(clk),方向控制(dir),清零

(clr)以及数据输入(din)。

2,用实验平台上的LED发光阵列的LED1~LED8显示并行数据的

输出。

三、实验内容:

通过VHDL编程,实现双向移位寄存器,要求有一个方向控制端,

一个脉冲输入,一个异步清零端,一个数据输入端以及8位的数

据输出端。

1. 打开QuartusII软件,建立一个新的工程。

2. 建立VHDL文件。

3. 建立矢量波形文件。

4. 进行功能仿真。

5. 进行时序仿真。

6. 器件的下载。

四、实验条件:

1. WindowsXP操作系统

2. QuartusII EDA开发系统

3. 杭州康芯SOPC硬件开发平台

五、实验原理:

通过VHDL编程,实现双向移位寄存器,要求有一个方向控制端,

一个脉冲输入,一个异步清零端,一个数据输入端以及8位的数

据输出端。

双向移位寄存器 双向移位寄存器

具体的接口如下所示:

clk:移位寄存器时钟脉冲输入,上升沿有效。(www.61k.com]

din:串行数据输入端。

clr:异步清零信号,高电平有效。

dir:方向控制端,要求高电平右移,低电平左移。

dout[7..0]:8位数据并行输入端。

硬件设置原理:

根据要求设置个端口,键7为时钟控制端,键8为数据输入端,键1为方向控制端,键5为异步清零。用LED发光阵列的LED1~LED8显示并行数据的输出,依次相对应为dout[7]……dout[0].根据模式7对应的开发系统I/O管脚映射表以及I/O模式7示意图为每一个端口指定引脚。

调试原理:

软件调试:

1、 当设置为左移时,低位依次将自己的值给高一位,最后将din给q[0],然后将q赋值给dout;

2、 当设置为右移时,高位依次将自己的值给低一位,最后将din给q[7],然后将q赋值给dout;

3、 观察结果是否符合结果。在验证结果时,首先进行功能仿真,观察结果,调试程序,在进行时序仿真。

硬件调试:

根据端口对应设置端口,设置dir值和输入,观察LED1~LED8改变是否和要求一致;再设置键5异步清零端,观察LED1~LED8的

双向移位寄存器 双向移位寄存器

变化。[www.61k.com]

六、源代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity d_reg is

port(clk,din,clr,dir:in std_logic;

dout:out std_logic_vector(7 downto 0)); end entity d_reg;

architecture one of d_reg is

begin

process(clr,clk)

variable q:std_logic_vector(7 downto 0);

begin

if(clr='1')then

dout<="00000000";

elsif(clk'event and clk='1')then

if(dir='1')then

for i in 1 to 7 loop

q(i-1):=q(i);

end loop;

q(7):=din;

dout<=q;

elsif(dir='0')then

for i in 6 downto 0 loop

q(i+1):=q(i);

end loop;

q(0):=din;

dout<=q;

end if;

end if;

end process;

end architecture one;

双向移位寄存器 双向移位寄存器

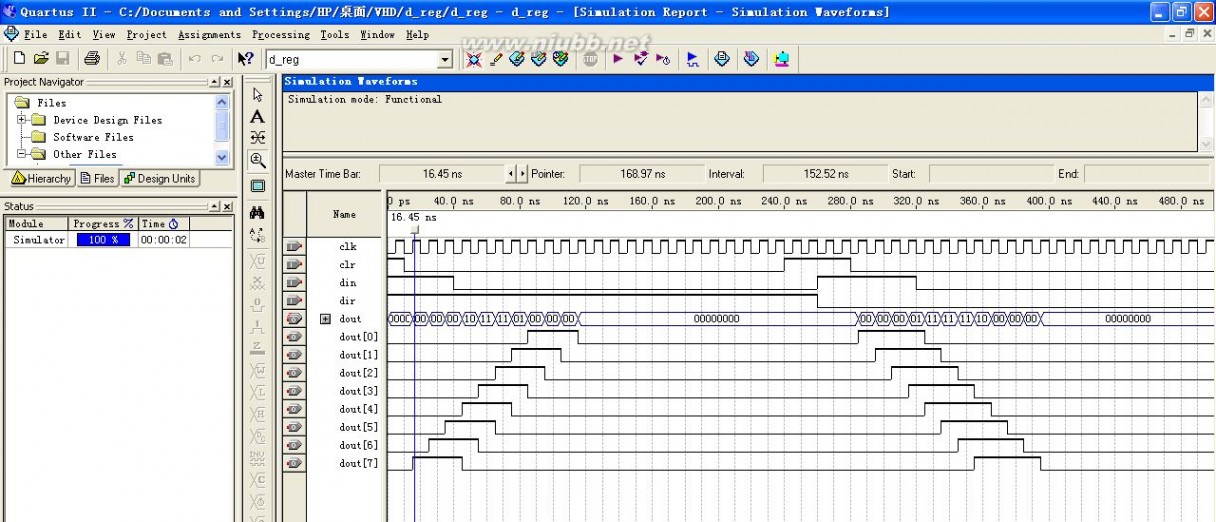

七、实验结果与分析: 1,功能仿真

2,时序仿真

双向移位寄存器 双向移位寄存器

说明:当输入为“1”,并且方向设置为“左”时,两次时钟脉冲控制之后的数据移位情况。(www.61k.com]

说明:输入为“0”时,再经过两个时钟脉冲移位之后的移位情况。

双向移位寄存器 双向移位寄存器

说明:再把方向设置为“右”时,一次时钟脉冲控制之后的数据移位情况。[www.61k.com)

八、讨论和回答问题及体会:

1.实验室的QuartusII在第一次不能进行下载调试。通过安装相应的证书文件解决了上述问题。

2.在进行编译的时候,使用了较多的if循环嵌套判断语句,会导致了仿真波形处出现了很大的延迟。改为使用case语句,降低了延迟,达到比较好的波形仿真效果。

3.安装驱动程序,此USB设备的驱动处于QuartusII安装目录中的driversusb-blaster中,进行USB装载连接。

4通过使用VHDL对双向移位寄存器的编写可以更加深刻的了解其功能。在编写过程中对VHDL语言程序得到了加深和熟悉,巩固了所学的知识。

本文标题:双向移位寄存器-8位双向移位寄存器电路设计61阅读| 精彩专题| 最新文章| 热门文章| 苏ICP备13036349号-1