一 : 实验六移位寄存器的设计

实验六 移位寄存器的设计

一、实验目的

1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。[www.61k.com]

2、熟悉移位寄存器的应用 — 实现数据的串行、并行转换和构成环形计数器。

二、实验预习要求

1、复习有关寄存器及串行、并行转换器有关内容。

2、查阅CC40194、CC4011及CC4068 逻辑线路。熟悉其逻辑功能及引脚排列。

3、在对CC40194进行送数后,若要使输出端改成另外的数码,是否一定要使寄存器清零?

4、使寄存器清零,除采用CR输入低电平外,可否采用右移或左移的方法?可否使用并行送数法?若可行,如何进行操作?

5、若进行循环左移,图6-4接线应如何改接?

6、画出用两片CC40194构成的七位左移串 / 并行转换器线路。

7、画出用两片CC40194构成的七位左移并 / 串行转换器线路。

三、实验设备及器件

1、 +5V直流电源 2、 单次脉冲源

3、 逻辑电平开关 4、 逻辑电平显示器

5、 CC40194×2(74LS194) CC4011(74LS00) CC4068(74LS30)

四、设计方法与参考资料

1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。

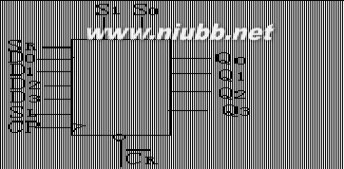

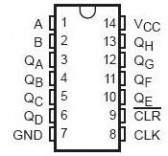

本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图6-1所示。

其中 D0、D1 、D2 、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;SR 为右移串行输入端,SL 为左移串行输入端;S1、S0 为操作模式控制端;CR为直接无条件清零端;

移位寄存器设计 实验六移位寄存器的设计

图6-1 CC40194的逻辑符号及引脚功能

CP为时钟脉冲输入端。(www.61k.com)

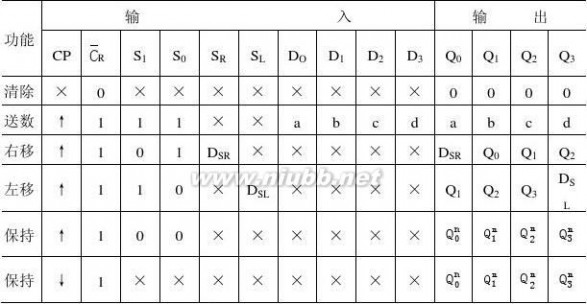

CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0→Q3),左移(方向由Q3→Q0),保持及清零。

S1、S0和CR端的控制作用如表6-1。

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累

加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。

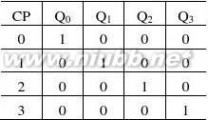

(1) 环形计数器

把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,

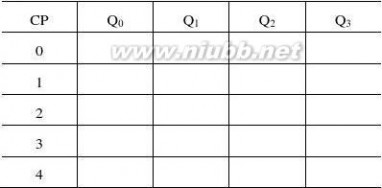

如图6-2所示,把输出端 Q3 和右移串行输入端SR 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→??,如表6-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图6-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 表6-2

移位寄存器设计 实验六移位寄存器的设计

图 6-2 环形计数器

如果将输出QO与左移串行输入端SL相连接,即可达左移循环移位。(www.61k.com)

(2)实现数据串、并行转换

① 串行/并行转换器

串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。

图6-3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位串/并行数据转换电路。

图6-3 七位串行 / 并行转换器

电路中S0端接高电平1,S1受Q7控制,二片寄存器连接成串行输入右移工作模式。Q7是转换结束标志。当Q7=1时,S1为0,使之成为S1S0=01的串入右移工作方式,当Q7=0时,S1=1,有S1S0=10,则串行送数结束,标志着串行输入的数据已转换成并行输出了。

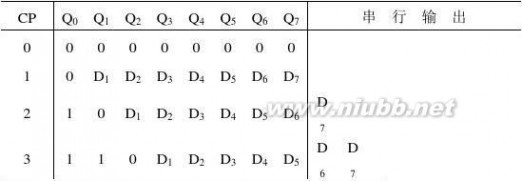

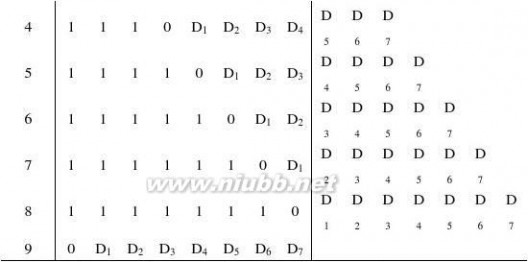

串行/并行转换的具体过程如下: 转换前,CR端加低电平,使1、2两片寄存器的内容清0,此时S1S0=11,寄存器执行并行输入工作方式。当第一个CP脉冲到来后,寄存器的输出状态Q0~Q7为01111111,与此同时S1S0变为01,转换电路变为执行串入右移工作方式,串行输入数据由1片的SR端加入。随着CP脉冲的依次加入,输出状态的变化可列成表6-3所示。

由表6-3可见,右移操作七次之后,Q7变为0,S1S0又变为11,说明串行输入结束。这时,串行输入的数码已经转换成了并行输出了。

当再来一个CP脉冲时,电路又重新执行一次并行输入,为第二组串行数码转换作好了准备。

② 并行/串行转换器

并行/串行转换器是指并行输入的数码经转换电路之后,换成串行输出。

图6-4是用两片CC40194(74LS194)组成的七位并行/串行转换电路,它比图6-3多了两只与非门G1和G2,电路工作方式同样为右移。

表6-3

移位寄存器设计 实验六移位寄存器的设计

图6-4 七位并行 / 串行转换器

寄存器清“0”后,加一个转换起动信号(负脉冲或低电平)。(www.61k.com]此时,由于方式控制S1S0

为11,转换电路执行并行输入操作。当第一个CP脉冲到来后,Q0Q1Q2Q3Q4Q5Q6Q7 的状态为0D1D2D3D4D5D6D7,并行输入数码存入寄存器。从而使得G1输出为1,G2输出为0,结果,S1S2变为01,转换电路随着CP脉冲的加入,开始执行右移串行输出,随着CP脉冲的依次加入,输出状态依次右移,待右移操作七次后,Q0~Q6的状态都为高电平1,与非门G1输出为低电平,G2门输出为高电平,S1S2又变为11,表示并/串行转换结束,且为第二次并行输入创造了条件。转换过程如表6-4所示。

中规模集成移位寄存器,其位数往往以4位居多,当需要的位数多于4位时,可把几片移位寄存器用级连的方法来扩展位数。

移位寄存器设计 实验六移位寄存器的设计

1、环形计数器

自拟实验线路用并行送数法予置寄存器为某二进制数码(如0100),然后进行右移循环,观察寄存器输出端状态的变化,记入表6-5中。[www.61k.com] 2、数据的串、并行转换 (1)串行输入、并行输出

按参考图6-3接线,进行右移串入、并出实验,串入数码自定;改接线路用左移方式实现并行输出。自拟表格,记录之。

(2)并行输入、串行输出

参考图6-4接线,进行右移并入、串出实验,并入数码自定。再改接线路用左移方式实现串行输出。自拟表格,记录之。 六、实验报告

1、分析表6-4的实验结果,总结移位寄存器CC40194的逻辑功能并写入表格功能总结一栏中。

1、 根据实验内容2 的结果,画出4位环形计数器的状态转换图及波形图。 2、 分析串 / 并、并 / 串转换器所得结果的正确性。

二 : 实验七 8位移位寄存器的设计

数字电路与逻辑设计实验报告

实验七 8位移位寄存器的设计

一、实验目的

熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言设计一个8位移位寄存器

二、实验内容

1.用VHDL语言设计由边沿触发式D触发器构成的8位移位寄存器,并进行仿真与分析;

三、实验原理

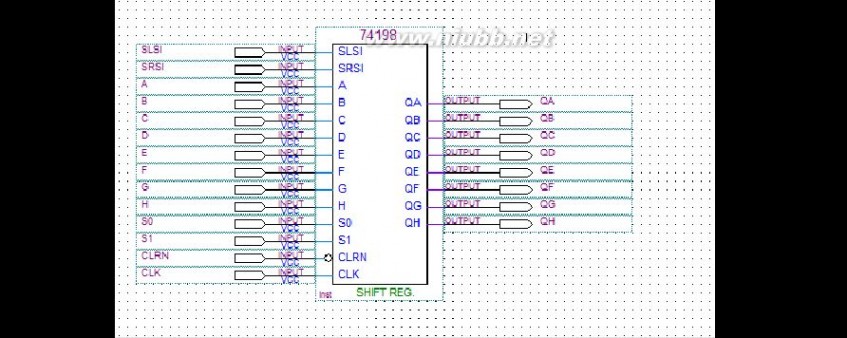

1.(1)8位移位寄存器逻辑电路的原理:

可以实现串行输出、并行输入,串行输出的功能。(www.61k.com)是能暂时存放二进制码的电路,被广泛的应用于各类数字系统和数字计算机中。寄存器的特点是存数方便。

abcdefgh为8个并行输入端,qa~qh为并行输出端,srsi为右移串行输入

端,slsi为左移串行输入端,s1,s0为模式控制端,clrn为异步清零端,clk为时钟脉冲输入端 (2)

通过实验实现逻辑的原理:

输入信号 输出信

号

clk clrn S1 S0 sl sr abcdefQ_abcde

gh fgh

1 1 1 0 0 00001100001111 ↑ 11

第 1 页 共 8 页

8位移位寄存器 实验七 8位移位寄存器的设计

数字电路与逻辑设计实验报告

↑ ↑ ↑ ↑ ↑ ↑ ↑ ↑ ↑ ↑

1 1 1 1 1 1 1 1 1 0

1 1 1 1 0 0 0 0 0 0

0 0 0 0 0 1 1 1 1 0

1 1 0 0 0 0 0 0 0 0

0 0 0 0 0 1 1 0 0 0

00001111 00011111 00111111 01111110 11111100 11111100 11111110 11111111 01111111 00111111

00011111 00111111 01111110 11111100 11111100 11111110 11111111 01111111 00111111 00000000

四、实验方法与步骤 实验方法:

采用基于FPGA进行数字逻辑电路设计的方法。[www.61k.com) 采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

实验步骤:

1、 编写源代码。打开QuartusⅡ软件平台,点击File中得New建立一个文件。编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。VHDL设计源代码如下:

第 2 页 共 8 页

8位移位寄存器 实验七 8位移位寄存器的设计

数字电路与逻辑设计实验报告

第 3 页 共 8 页

8位移位寄存器 实验七 8位移位寄存器的设计

数字电路与逻辑设计实验报告

2、按照实验箱上FPGA的芯片名更改编程芯片的设臵。(www.61k.com]操作是点击

Assign/Device,选取芯片的类型“Altera的EPF10K20TI144_4”

3、编译与调试。

确定源代码文件为当前工程文件,点击Complier进行文件编译。编译结果有错误或警告,则将要调试修改直至文件编译成功。

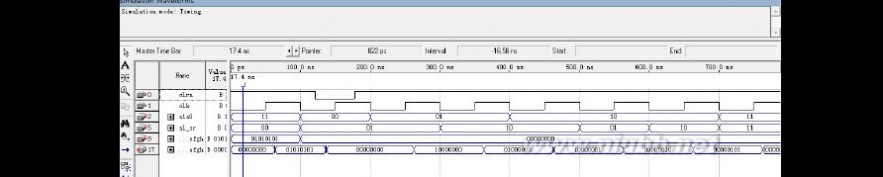

4、波形仿真及验证。

在编译成功后,点击Waveform开始设计波形。点击“insert the node”,按照程序所述插入clrn,clk,s0,s1,sl,sr,a,b,c,d,e,f,g,h,qa,qb,qc,qd,qe,qf,qg,qh共22个节点(clrn,clk,s0,s1,sl,sr, a,b,c,d,e,f,g,h为输入节点,qa,qb,qc,qd,qe,qf,qg,qh为输出节点)。设臵s0,s1,sl,sr以不同的信号输入,abcdefgh输入初始数据,clk为时钟信号,点击保存按钮保存。然后进行功能仿真,选择菜单Processing->Generate Functional Netlist命令产生功能仿真网表,选择菜单Assignments-->Setting下拉列表中选择Simulator input ,在右侧的Simulation mode下拉列表中选择Functional,完成设臵;选择菜单中的 Processing->Start Simulation启动功能仿真,然后查看波形报告中的结果

5、时序仿真。首先进行全编译,编译成功后,点击Assignments 的settings的 simulation mode: Timing,仿真成功后即出带延时的波形图。

6、FPGA芯片编程及验证。

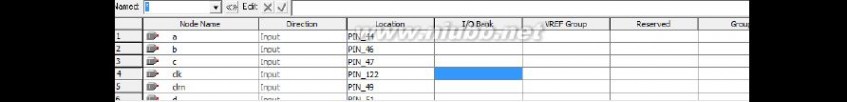

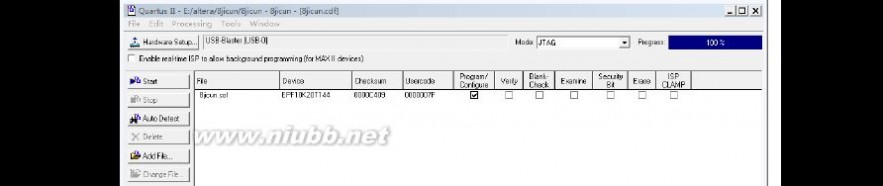

(1)分配管脚:assignment—>Pins在Location中选择合适的输入输出管脚并进行编译。

(2)下载验证:Tools->Programmer进入下载窗口Hardware

Setup

第 4 页 共 8 页

8位移位寄存器 实验七 8位移位寄存器的设计

数字电路与逻辑设计实验报告

—>ByteBlaster->Start->OK

(3)初始化电路,根据设臵好的管脚资源擦做实验电路板,完成数据测试。[www.61k.com]

五、实验结果与分析

1、 编译过程

a)编译过程、调试结果

b)结果分析及结论:编译无错误,可进行下一步

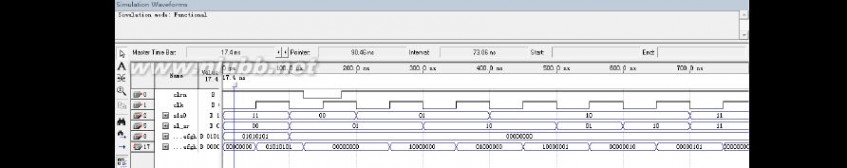

2、 功能仿真

a)功能仿真过程及仿真结果

b)结果分析及结论:

最开始是清零;

臵数:当clrn=1时,S=11,输入01010101,输出01010101;

再清零,

右移:当S=01时,slsr=01时补1,因此输出10000000;

slsr=10时补0,因此输出01000000;

左移:当S=10时,slsr=10时补1,输出为10000001;

slsr=01补0,输出为00000010;

第 5 页 共 8 页

8位移位寄存器 实验七 8位移位寄存器的设计

数字电路与逻辑设计实验报告

slsr=10时补1,输出为00000101;

3、 时序仿真

a)时序仿真过程及仿真结果

b)结果分析及结论: 仿真结果与逻辑存在偏差,因为时序仿真存在延迟现象,是正常现象。(www.61k.com)

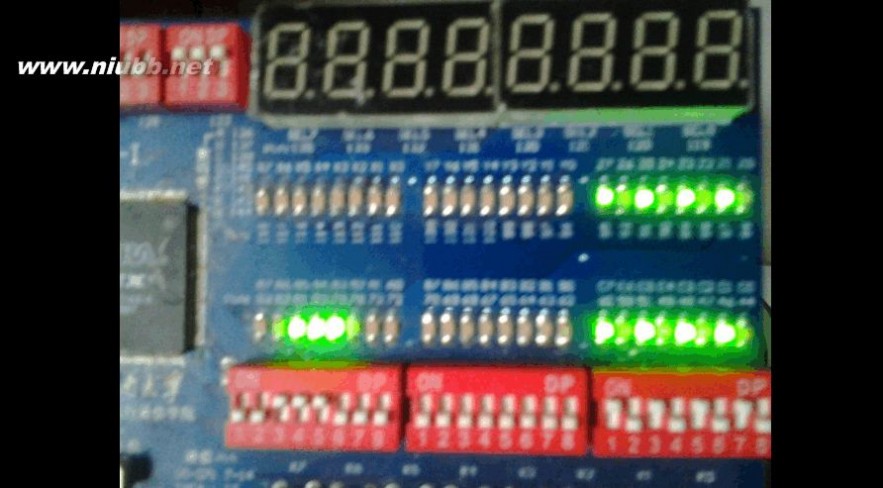

4、 Programming芯片编程

a)芯片编程过程

b)编程芯片FPGA验证结果 b)结果分析与结论

按图示顺序为

右移补一:

清零:

臵数为01010101:

第 6 页 共 8 页

8位移位寄存器 实验七 8位移位寄存器的设计

数字电路与逻辑设计实验报告

第 7 页 共 8 页

8位移位寄存器 实验七 8位移位寄存器的设计

数字电路与逻辑设计实验报告

由于没有在代码中加入保持的代码,所以不能抓拍到所有的结果,信号变

化的太快。(www.61k.com)

六、实验结论

1.实验结论:成功参照74198芯片,用VHDL语言设计由边沿触发式D触发器构成的8位移位寄存器,并进行仿真与分析;根据功能仿真和时序仿真的波形图显示成功,且下载成功。

2.实验心得:移位寄存器通过对数据的移动来储存数据,存数方便,但是范围较小,要弄懂移位寄存器的原理首先要搞懂它的逻辑功能表,如此才能在仿真过程中了解结果的正确与否,然后有一段缺陷是没有在代码中加入保持的功能,在下载时结果变化的太快,导致不能抓拍到所有的变化结果。下载过程耗费了太多的时间,都是自己不熟悉过程导致的。以后会多加练习下载这一部分。

第 8 页 共 8 页

三 : 8位移位寄存器的设计

数字电路与逻辑设计实验报告

实验七8位移位寄存器的设计

班级 信息安全2班 姓名 张亮 学号20110806228

一、实验目的

熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言设计8位移位寄存器。并且掌握组合逻辑电路的功能测试和时序仿真;学会运用逻辑图设计电路。

二、实验内容

用VHDL语言设计由边沿触发式D触发器构成的8位串入并出移位寄存器,并进行仿真与分析; (查找相应资料)

三、实验原理

? 逻辑电路的原理

8位移位寄存器的设计

在数字电路中,用来存放二进制数据或代码的电路称为寄存器。寄存器是由具有存储功能的触发器组合起来构成的。一个触发器可以存储一位二进制代码,存放N位二进制代码的寄存器,需用n个触发器来构成。按功能可分为:基本寄存器和移位寄存器。移位寄存器中的数据可以在移位脉冲作用下一次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

目前常用的集成移位寄存器种类很多,如74164、74165、74166、74595均为八位单向移位寄存器,74195为四位单向移存器,74194为四位双向移存器,74198为八位双向移存器。

逻辑图如图所示:

逻辑功能表

? 通过实验实现逻辑的原理

8位移位寄存器的设计

在CMOS移位寄存器中,有的品种只具有串行或并行中的一种输入方式,但也有些品种同时兼有串行和并行两种输入方式。串行输入的数据加到第一个寄存单元的D端,在时钟脉冲的作用下输入,数据传送速度较慢;并行输入的数据一般由寄存单元的R、S端送入,传送速度较快。移位

第 1 页 共 7 页

数字电路与逻辑设计实验报告

寄存器的移位方向有右移和左移之分。右移是指数据由左边最低位输入,依次由右边的最高位输出;左移时,右边的第一位为最低位,最左边的则为最高位,数据由低位的右边输入,由高位的左边输出。

四、实验方法与步骤

实验方法:

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII 软件仿真平台。

实验步骤:

1、编写源代码。打开QuartusII软件平台,点击File中得New建立一个文件。编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

2、编译与调试。确定源代码文件为当前工程文件,点击Complier进行文件编译。编译结果有错误或警告,则将要调试修改直至文件编译成功。

3、波形仿真及验证。在编译成功后,点击Waveform开始设计波形。点击“insert the node”,按照程序所述插入节点(具体节点根据不同实验的变量而定)。任意设臵输入节点的输入波形…点击保存按钮保存。

五、实验结果与分析

A. 编译过程

8位移位寄存器的设计

a)源代码(VHDL设计)

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY shifter IS PORT

(

data_in : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输入的数据

n : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位的数量

dir : IN STD_LOGIC; --移动的方向 0:左 1:右

kind : IN STD_LOGIC_VECTOR(1 DOWNTO 0); --移动类型 00:算术移 01:逻辑移 10:循环移

clock : IN BIT; --手动时钟PULSE

data_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --移位的结果

);

END shifter;

ARCHITECTURE behav of shifter IS

BEGIN

PROCESS (data_in, n, dir, kind)

VARIABLE x,y : STD_LOGIC_VECTOR(7 DOWNTO 0);

VARIABLE ctrl0,ctrl1,ctrl2 : STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF (clock'EVENT AND clock = '1')

THEN --产生控制向量ctrl

ctrl0 := n(0) & dir & kind(1) & kind(0);

ctrl1 := n(1) & dir & kind(1) & kind(0);

ctrl2 := n(2) & dir & kind(1) & kind(0);

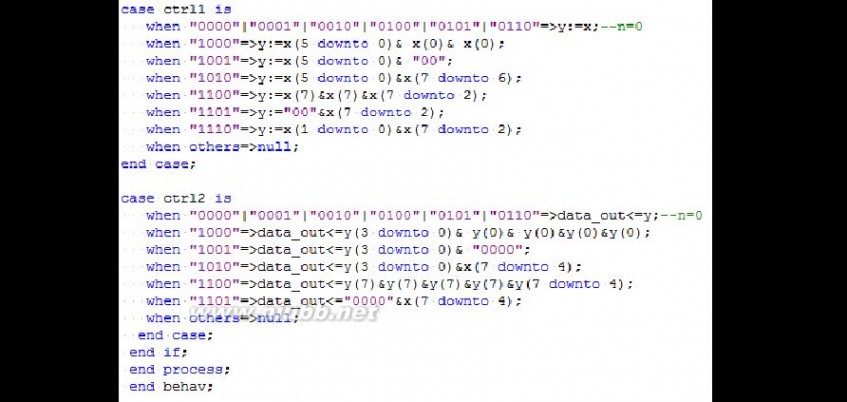

CASE ctrl0 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => x := data_in; --n=0时不移动 WHEN "1000" => x := data_in(6 DOWNTO 0) & data_in(0); --算术左移1位

WHEN "1001" => x := data_in(6 DOWNTO 0) & '0'; --逻辑左移1位

WHEN "1010" => x := data_in(6 DOWNTO 0) & data_in(7); --循环左移1位

第 2 页 共 7 页

数字电路与逻辑设计实验报告

WHEN "1100" => x := data_in(7) & data_in(7 DOWNTO 1); --算术右移1

位

WHEN "1101" => x := '0' & data_in(7 DOWNTO 1); --逻辑右移1

位

WHEN "1110" => x := data_in(0) & data_in(7 DOWNTO 1); --循环右移1

位

WHEN others => null;

END CASE;

CASE ctrl1 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => y := x; --n=0时不移动 WHEN "1000" => y := x(5 DOWNTO 0) & x(0) & x(0); --算术左移

2位

WHEN "1001" => y := x(5 DOWNTO 0) & "00"; --逻辑左

移2位

WHEN "1010" => y := x(5 DOWNTO 0) & x(7 DOWNTO 6); --循环

左移2位

WHEN "1100" => y := x(7) & x(7) & x(7 DOWNTO 2); --算术右移

2位

WHEN "1101" => y := "00" & x(7 DOWNTO 2); --逻辑右

移2位

WHEN "1110" => y := x(1 DOWNTO 0) & x(7 DOWNTO 2); --循环右

移2位

WHEN others => null;

END CASE;

CASE ctrl2 IS

WHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => data_out <= y; --n=0时不移动

WHEN "1000" => data_out <= y(3 DOWNTO 0) & y(0) & y(0) & y(0) & y(0); --算术左移4位 WHEN "1001" => data_out <= y(3 DOWNTO 0) & "0000"; --逻辑左

移4位

WHEN "1010" | "1110" => data_out <= y(3 DOWNTO 0) & y(7 DOWNTO 4); --循环左

(右)移4位

WHEN "1100" => data_out <= y(7) & y(7) & y(7) & y(7) & y(7 DOWNTO 4); --算术右移4位 WHEN "1101" => data_out <= "0000" & y(7 DOWNTO 4); --逻辑右移

4位

WHEN others => null;

END CASE;

END IF;

END PROCESS;

END behav;

逻辑图(部分):

第 3 页 共 7 页

数字电路与逻辑设计实验报告

b)编译、调试过程

c)结果分析及结论

第 4 页 共 7 页

61阅读| 精彩专题| 最新文章| 热门文章| 苏ICP备13036349号-1