一 : VHDL之一位全减器

一位全减器实验

实验目的:1.首先设计一位半减器, 然后设计出半减器,diff是输出差,s_out是借位输出,sub_in是借位输入。(www.61k.com)半减器的实验程序为:

library ieee;

use ieee.std_logic_1164.all;

entity h_suber is

port (x,y : in std_logic;

diff,s_out : out std_logic );

end h_suber ;

architecture hdlarch of h_suber is

begin

process(x,y) begin diff <= x xor y; s_out <= (not x) and y; end process;

end hdlarch;

2.以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计(减法运算是 x – y - sun_in = diffr)。以一位半减器为实体,生成器件,连接如下图的电路,使之构成以为全减器

实验仿真波形:

一位全减器 VHDL之一位全减器

(www.61k.com)一位全减器 VHDL之一位全减器

四位全减器实验

1.实验原理:(1)利用前面设计的全减器(一位全减器)生成元件;

(2)建立新的原理图,完成4位全减器的设计;

(3)进行波形仿真验证;

2.实验仿真波形图:

一位全减器 VHDL之一位全减器

7段数码显示译码器设计

1、实验目的:学习7段数码显示译码器设计、多层次设计方法、和总线数据输入方式的仿真,并进行电路板下载验证。(www.61k.com]

2、实验原理:7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用VHDL译码程序在FPGA或CPLD中实现。本项实验很容易实现这一目的。例2作为7段BCD码译码器的设计,输出信号LED7S的7位分别接如实验图2数码管的7个段,高位在左,低位在右。例如当LED7S输出为 "1101101" 时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1,接有高电平的段发亮,于是数码管显示“5”。

3、实验内容:说明例2中各语句的含义,以及该例的整体功能。在QUARTUS II上对以下该例进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形(提示:用输入总线的方式给出输入信号仿真数据)。

试验程序:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY DecL7S IS

PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ;

LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ;

END ;

ARCHITECTURE one OF DecL7S IS

BEGIN

PROCESS( A )

BEGIN

CASE A(3 DOWNTO 0) IS

WHEN "0000" => LED7S <= "0111111" ; -- X“3F”?0

WHEN "0001" => LED7S <= "0000110" ; -- X“06”?1

WHEN "0010" => LED7S <= "1011011" ; -- X“5B”?2

WHEN "0011" => LED7S <= "1001111" ; -- X“4F”?3

WHEN "0100" => LED7S <= "1100110" ; -- X“66”?4

WHEN "0101" => LED7S <= "1101101" ; -- X“6D”?5

WHEN "0110" => LED7S <= "1111101" ; -- X“7D”?6

WHEN "0111" => LED7S <= "0000111" ; -- X“07”?7

WHEN "1000" => LED7S <= "1111111" ; -- X“7F”?8

WHEN "1001" => LED7S <= "1101111" ; -- X“6F”?9

WHEN "1010" => LED7S <= "1110111" ; -- X“77”?10

WHEN "1011" => LED7S <= "1111100" ; -- X“7C”?11

WHEN "1100" => LED7S <= "0111001" ; -- X“39”?12

WHEN "1101" => LED7S <= "1011110" ; -- X“5E”?13

WHEN "1110" => LED7S <= "1111001" ; -- X“79”?14

WHEN "1111" => LED7S <= "1110001" ; -- X“71”?15

WHEN OTHERS => NULL ;

END CASE ;

一位全减器 VHDL之一位全减器

END PROCESS ;

END ;

4.实验原理图和仿真波形:

二 : 一位全加全减器的实现

课程实验报告

课程名称:数字电路与逻辑设计

专业班级:计实1001班

学 号:U201014488

姓 名:王宸敏 指导教师:唐九飞

周 次:第九周 同组人员:熊凯

报告日期:2012年4月18日

一位全减器 一位全加全减器的实现

计算机科学与技术学院

【内容A】

一、 实验名称

一位全加/全减器的实现

二、 实验目的

1. 掌握组合逻辑电路的功能测试

2. 验证半加器和全加器的逻辑功能

3. 学会二进制数的运算规律

三、 实验所用仪器和组件

1. 二输入四“与非”门1片,型号为74LS00

2. 三输入三“与非”门1片,型号为74LS10

3. 二输入四“异或”门1片,型号为74LS86

四、 实验设计方案及逻辑图

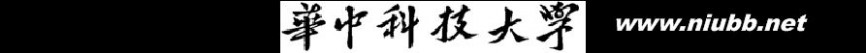

首先根据真值表得到了其卡诺图如下所示:

根据输入与输出写出全加/减法器的函数表达式,如下: 实现全加法器的表达式:

M?0时,S?A?B?Cin

CO?AB?ACin?BCin?AB?ACin?BCin; 实现全减法器的表达式:

M?1

时,S?A?B?Cin

CO?AB?ACin?BCin?AB?ACin?BCin.

一位全减器 一位全加全减器的实现

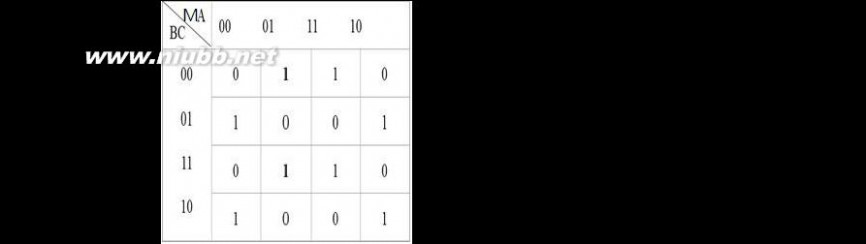

由表达式可知:S采用异或的逻辑门而Co则采用与非的逻辑门得到,因此画出逻辑图如下:

五、 实验记录

六、 描述实验现象,并运用所学的知识进行分析、处理及讨论

1. 在m=0时,在输入端输入三个电平时,输出实现了全加器的功能,即把三个输入当作

被加数、加数和低位的进位,同时两个输出分别表示了和与低位的进位。[www.61k.com) 2. 在m=1时,在输入端输入三个电平时,输出实现了全减器的功能,即把三个输入当作

被减数、减数和低位的借位,同时两个输出分别表示了差与高位的借位。 因为电路的设计是根据真值表的结果得到的,通过真值表画出卡诺图从而的到输出关于输入的表达式,因此他所实现的功能正是我们所需要的全加器与全减器的功能,只不过是通过逻辑门进行了处理,得到的是正确的值。

一位全减器 一位全加全减器的实现

【内容C】

一、 实验名称

舍入与检测电路的设计

二、 实验目的

1. 掌握组合逻辑电路的功能测试

2. 验证半加器和全加器的逻辑功能

3. 学会二进制数的运算规律

三、 实验所用仪器和组件

1. 六门反向器组件1片,型号为74LS04

2. 二输入四“与非”门组件1片,型号为74LS00

3. 三输入三“与非”门组件1片,型号为74LS10

4. 二输入四“异或”门组件1片,型号为74LS86

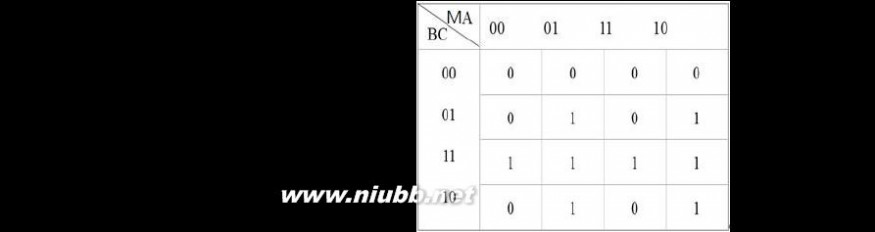

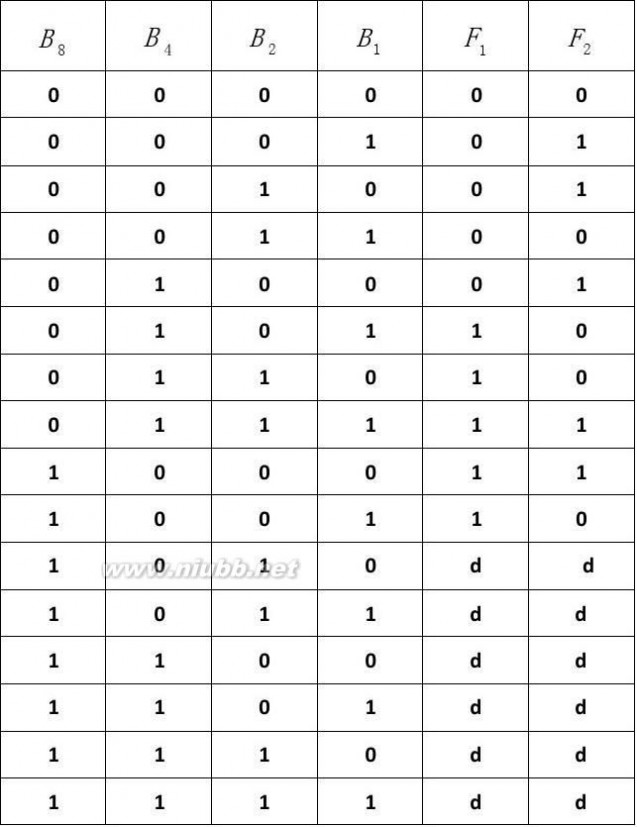

四、 实验设计方案及逻辑图 根据题意,输入为8421码,F1表示“四舍五入”电路的输出,其卡诺图如下:

由卡诺图可得到其函数表达式,并且经过化简如下:

F1?B8?B4B2?B4B1?B8?B4B2?B4B1

因此,根据表达式可以设计电路图如下所示:

一位全减器 一位全加全减器的实现

同理,可以容易分析得到卡诺图如下:

输出F2的表达式,如下:

F2?B8?B4?B2?B1

由表达式,得到逻辑电路如下:

五、 实验记录

一位全减器 一位全加全减器的实现

六、 描述实验现象,并运用所学的知识进行分析、处理及讨论

1.

对于“四舍五入”电路,当输入的8421码小于等于4时,即0000,0001,0010,0011,0100这五种状态,显示灯不亮,表示输出为0;当输入的8421码大于等于5时,即0101,0110,0111,1000,1001这五种状态,显示灯亮,表示输出2.

为1.

对于输入的1的个数的电路,当输入的1的个数为奇数时,即0001,0010,0100,

一位全减器 一位全加全减器的实现

0111,1000这五种状态,显示灯亮,表示输出为1;当输入的1的个数为偶数时,即0000,0011,0101,0110,1001这五种状态,显示灯不亮,表示输出为0.

当四个输出进入所对应的逻辑门电路后,根据之前的真值表、卡诺图及表达式,得到了正确的输出状态,在这里逻辑门电路就是让输入完成得到正确的输出结果。(www.61k.com)

七、 回答思考题

1. 化简包含无关条件的逻辑函数时应该注意什么?

答:有无关条件的逻辑函数时,应先作出其卡诺图,根据表达式最简的这一要求将无关条件任意的置0或置1,总之,是要把表达式化作最简。

2. 多输出逻辑函数化简时应注意什么?

答:多输出的逻辑函数化简时,应分别针对某一输出化简得到关于输入的最简表达式。

3. 你所设计的电路是否达到了最简?为什么?

答:显然达到了最简。我设计的电路的最简表达式是根据卡诺图得到了,因为再找卡诺图的必要最小质蕴含项时是正确的,因此得到的表达式是最简的,从而设计的逻辑电路也是最简的。

三 : 一位全减器

实验一 1位二进制全减器设计

一、实验目的

1.熟悉Quartes II集成开发软件的使用; 2.初步熟悉PH-1V型实验装置的使用;

3 . 学习用原理图输入法和文本输入法进行简单的数字电路设计,掌握系统仿真,学会分析硬件测试结果。[www.61k.com)

二、实验内容与要求

1.采用原理图输入法和文本输入法分别实现,分层设计,底层由半减器(也用原理图输入法)和逻辑门组成;

2.建立波形文件,并进行系统仿真,用软件验证设计结果;

3. 在仿真正确的情况下,对1位二进制半加/减器分别下载到实验箱中做硬件测试

三、实验原理及设计思路

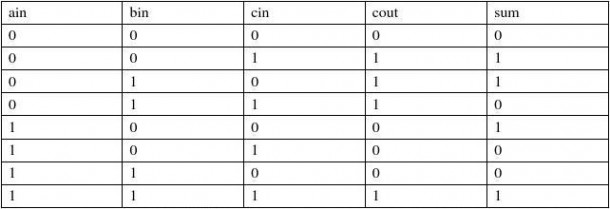

根据一位二进制全减器的工作原理,可得其真值表为(如下:cin表示低位向本位借位。cout表示本位向高位借位)

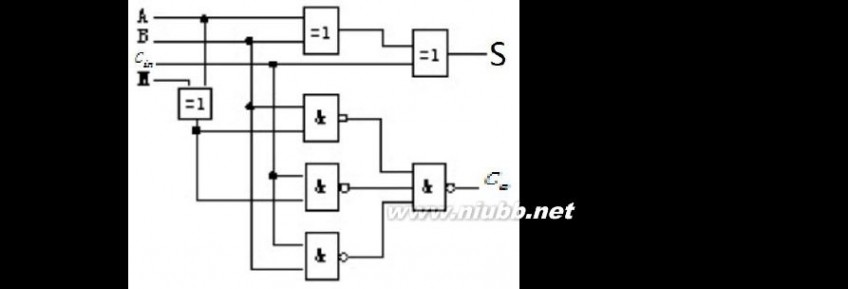

由EDA教程中全加器的顶层设计描述及半加器调用可类比到全减器的设计,可由先对半减器进行描述,然后进行两次调用。半减器的工作时的逻辑表达式为:so=a XOR b ; co=(NOT a)AND b

四、实验程序(程序来源:EDA技术实验教程)

LIBRARY IEEE ; ——或门逻辑描述 USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2a IS

PORT (a, b :IN STD_LOGIC;

c : OUT STD_LOGIC ); END ENTITY or2a;

ARCHITECTURE one OF or2a IS

一位全减器 一位全减器

BEGIN

c <= a OR b ;

END ARCHITECTURE one;

LIBRARY IEEE; ——半减器描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_suber IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_suber;

ARCHITECTURE fh1 OF h_suber is

BEGIN

so <= a xor b ;

co <= (not a )AND b ;

END ARCHITECTURE fh1;

LIBRARY IEEE; ——1位二进制全减器顶层设计描述

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_suber IS

PORT (ain,bin,cin : IN STD_LOGIC;

cout,sum : OUT STD_LOGIC );

END ENTITY f_suber;

ARCHITECTURE fd1 OF f_suber IS

COMPONENT h_suber ——调用半减器声明语句

PORT ( a,b : IN STD_LOGIC;

co,so : OUT STD_LOGIC);

END COMPONENT ;

COMPONENT or2a ——调用或门声明语句

PORT (a,b : IN STD_LOGIC;

c : OUT STD_LOGIC);

END COMPONENT;

SIGNAL d,e,f : STD_LOGIC; ——定义3个信号作为内部的连接线 BEGIN

u1 : h_suber PORT MAP(a=>ain,b=>bin,

co=>d,so=>e); ——例化语句

u2 : h_suber PORT MAP(a=>e, b=>cin,

co=>f,so=>sum);

u3 : or2a PORT MAP(a=>d, b=>f,c=>cout);

END ARCHITECTURE fd1 ;

五、 实验步骤:

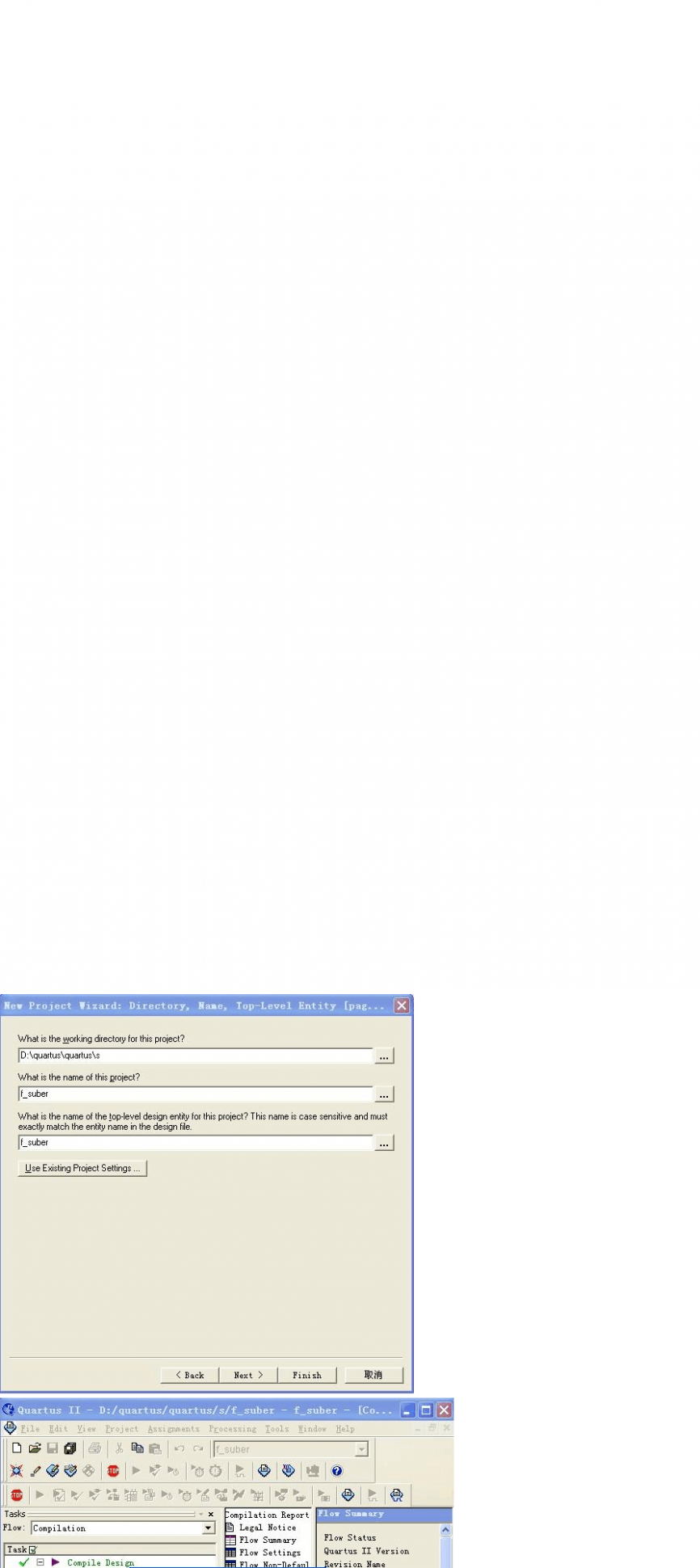

1.打开Quartes II软件,建立工程文件,注意工程名要与实体名一致:

一位全减器 一位全减器

2、打开QuartusII,选择菜单File->New->VHDL.File,建立vhdl文件,将以上程序输入并进行编译;

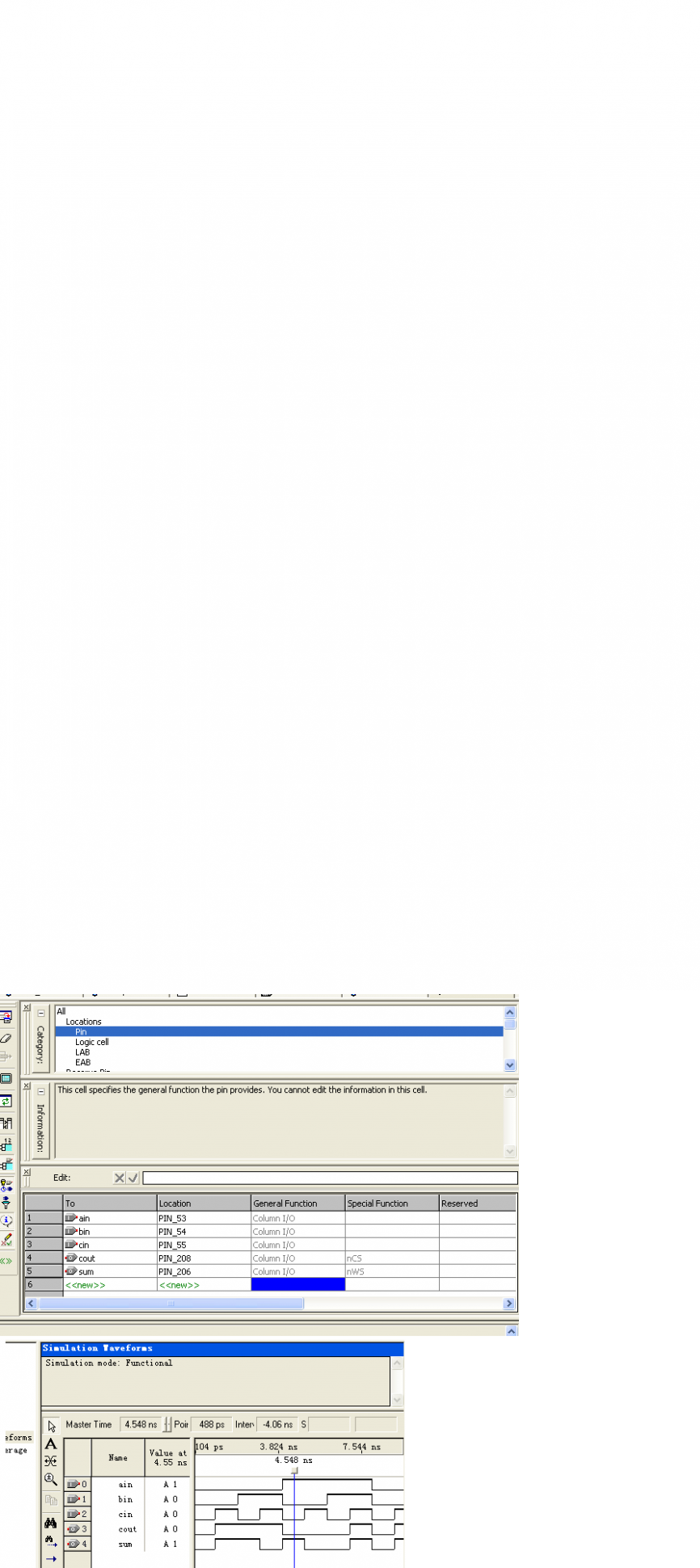

3、建立波形文件,并进行系统仿真,注意设置仿真结束时间以及添加结点;

一位全减器 一位全减器

4、输入信号波形Tools->Options->Waveform Editor,进行功能仿真Tools->Simulator Tools,在Simulator Mode选择Functional,仿真表生成后点击Start开始仿真,完成后点击Report结果

一位全减器 一位全减器

如下图所示;

5、引脚锁定,及设置流程

对各管脚进行分配,将ain分配给53,bin分配给54,cin分配给55。[www.61k.com)sum分配给208,Cout分配给206。选择菜单Assignment->Assignment Editor->Pin 窗口,选择菜单View->Show All Knowm Pin Names 进行引脚设置:

一位全减器 一位全减器

7、用下载线将计算机并口和实验箱上的JTAG口连接起来,接通电源;选择tool->programmer菜单,打开programmer窗口,在Mode中选择JTAG,选择好硬件设置,然后进行下载:

8、原理图输入法只需在第2步中建立 Block Diagrame/Schematic File,然后输入上述原理图,选择菜单File->create symbol file for current file项,将其变成元件符号存盘,在做全减器原理图时进行调用:

半减器原理图

:

全减器原理图:

一位全减器 一位全减器

六、硬件测试结果

在硬件试验箱上,按照真值表的值给出高、低电平,最后在LED8、LED7观察其亮灭情况,符合高电平亮,低电平灭的规律,表明实验成功。[www.61k.com)通过实验结果与真值表相符,实验成功。

七、实验心得

实验前,一定要做好实验预习,写好实验报告,事前写好设计项目的VHDL设计文件. 熟悉实验箱的用法,对实验设计过程的各个步骤要做到心中有数,遇到不理解的地方,一定要向同学或老师问清楚,明确各个具体的操作步骤和详细的过程.熟悉EDA设计的完整流程.仔细思考可能出现和已经出现的问题,独立解决.比如下载出现异常,如何处理.实验的时候出现这种情况,经过检查发现是接口有问题,更换后,能成功的下载和进行硬件测试,得到正确的结果.在此过程,做好引脚设置也是关键.

本文标题:一位全减器-VHDL之一位全减器61阅读| 精彩专题| 最新文章| 热门文章| 苏ICP备13036349号-1